## Embedded Multicore: An Introduction

EMBMCRM Rev. 0 07/2009

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support: http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, and StarCore and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. RapidIO is a registered trademark of the RapidIO Trade Association.

© Freescale Semiconductor, Inc., 2009. All rights reserved.

## Contents

## Paragraph Number

## Title

Page Number

## Chapter 1 Embedded Multicore, an Overview

| 1.1   | Why Multicore?                | 1-2 |

|-------|-------------------------------|-----|

| 1.2   | Different Types of Multicore  |     |

| 1.3   | Parallelism                   |     |

| 1.3.1 | Bit-Level Parallelism         | 1-6 |

| 1.3.2 | Instruction-Level Parallelism | 1-6 |

| 1.3.3 | Data Parallelism              | 1-6 |

| 1.3.4 | Task Parallelism              | 1-6 |

| 1.4   | System and Software Design    | 1-7 |

| 1.5   | Conclusion                    | 1-9 |

## Chapter 2 Embedded Multicore from a Hardware Perspective

| 2.1   | Multicore Devices                   | . 2-2 |

|-------|-------------------------------------|-------|

| 2.1.1 | Power Savings                       | . 2-5 |

| 2.1.2 | System-Level Stability and Security | 2-5   |

| 2.2   | From Coprocessors to Multiple Cores | . 2-6 |

| 2.2.1 | Internal Access                     | . 2-6 |

| 2.2.2 | Memory Hierarchy                    | . 2-8 |

| 2.2.3 | Interfaces                          |       |

| 2.2.4 | Debugging and Profiling             | . 2-9 |

| 2.3   | Conclusion                          |       |

## Chapter 3 Embedded Multicore: Software Design

| 3.1   | Amdahl's Law                                   |  |

|-------|------------------------------------------------|--|

| 3.2   | Gustafson's Law                                |  |

| 3.3   | Parallelism                                    |  |

| 3.4   | Symmetric and Asymmetric Multiprocessing       |  |

| 3.5   | Processes and Threads                          |  |

| 3.5.1 | Task and Process Mapping                       |  |

| 3.5.2 | Run to Completion                              |  |

| 3.5.3 | Interprocess Communication and Synchronization |  |

| 3.5.4 | Semaphores and Locks                           |  |

|       | -                                              |  |

## Contents

## Paragraph Number

## Title

## Page Number

## Chapter 4

## Embedded Multicore: SMP and Multithreading

| 4.1   | Introduction to Symmetric Multiprocessing   | 4-2  |

|-------|---------------------------------------------|------|

| 4.2   | Parallelized Application Designs            | 4-3  |

| 4.3   | Macro- and Microparallelization             |      |

| 4.3.1 | POSIX Threads                               | 4-4  |

| 4.3.2 | OpenMP                                      | 4-6  |

| 4.4   | Performance Constraints and Common Pitfalls |      |

| 4.5   | Summary                                     | 4-10 |

## Chapter 5 Embedded Multicore: SMP Operating Systems

| 5.1   | SMP Linux                          |  |

|-------|------------------------------------|--|

| 5.1.1 | Task Schedulers and Load Balancing |  |

| 5.1.2 | Core Affinity                      |  |

| 5.2   | Enea's OSE for Multicore           |  |

| 5.2.1 | Architecture Overview              |  |

| 5.2.2 | Various Multicore Models           |  |

| 5.2.3 | Enea OSE Advantages                |  |

| 5.3   | Conclusion                         |  |

## Chapter 6 Virtualization and the Hypervisor

| 6.1 | Virtualization—An Overview                  | 6-2 |

|-----|---------------------------------------------|-----|

| 6.2 | Privilege Levels, Addressing and Exceptions | 6-4 |

| 6.3 | Hardware Features to Improve Virtualization | 6-5 |

| 6.4 | Security and Protection between VMs         | 6-6 |

| 6.5 | Messaging Between VMs                       | 6-7 |

| 6.6 | Debugging and Run Control                   | 6-7 |

| 6.7 | Conclusions                                 |     |

## Chapter 7 Embedded Multicore: Virtual Platforms

| 7.1 | Simulation of Computer Systems         | 7-2 |

|-----|----------------------------------------|-----|

| 7.2 | Obtaining Hardware Early               |     |

| 7.3 | Using a Virtual Platform for Debugging |     |

| 7.4 | Multiprocessor Software Debugging      | 7-5 |

#### Embedded Multicore: An Introduction, Rev. 0

## Contents

| Paragraph<br>Number | Title                                       | Page<br>Number |

|---------------------|---------------------------------------------|----------------|

| 7.5                 | Using Virtual Platforms for Hardware Design |                |

| 7.5.1               | Execution Speed                             |                |

| 7.6                 | Conclusion                                  |                |

## About the Authors

## Figures

| Figure<br>Number | Title                                                                                          | Page<br>Number |

|------------------|------------------------------------------------------------------------------------------------|----------------|

| 1-1              | Improved Power Consumption as an Incentive for Multicore (MPC8641)                             |                |

| 1-2              | Heterogeneous and Homogeneous                                                                  |                |

| 1-3              | Memory Designs in Multiple CPU Systems                                                         |                |

| 1-4              | MPC7120 GPON Block Diagram                                                                     |                |

| 1-5              | Mix and Match                                                                                  |                |

| 2-1              | P4080 Block Diagram                                                                            |                |

| 2-2              | MSC8144 Block Diagram                                                                          |                |

| 2-3              | e500mc Block Diagram                                                                           |                |

| 2-4              | Single Bus vs. Switch Fabric                                                                   |                |

| 2-5              | Cache Stashing                                                                                 |                |

| 2-6              | Debug Interface                                                                                |                |

| 3-1              | Amdahl's Law: Speedup as a Function of Number of Cores                                         |                |

| 3-2              | Gustafson's Law                                                                                |                |

| 3-3              | Block Diagram of Router Application                                                            |                |

| 3-4              | Processes and Threads                                                                          |                |

| 3-5              | Using Semaphores to Protect a Critical Section                                                 |                |

| 3-6              | Network Routing Application                                                                    |                |

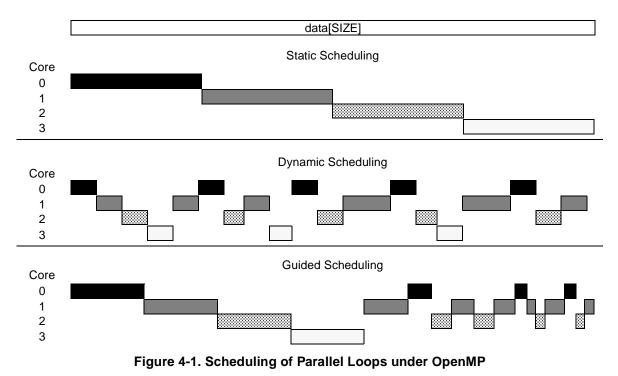

| 4-1              | Scheduling of Parallel Loops under OpenMP                                                      |                |

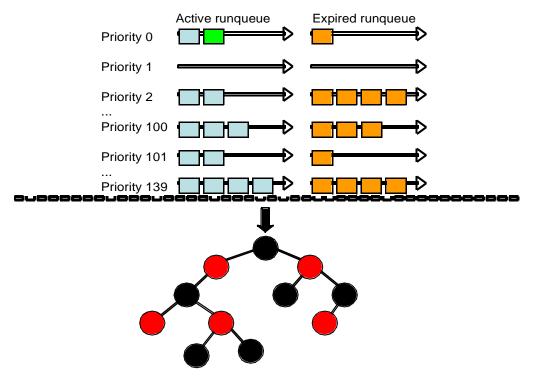

| 5-1              | Schedulers (Using a Red–Black Tree Structure)                                                  |                |

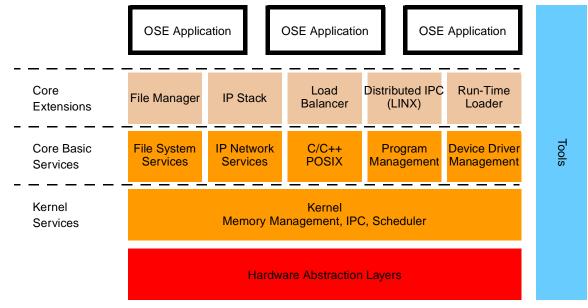

| 5-2              | Micro-kernel Architecture                                                                      |                |

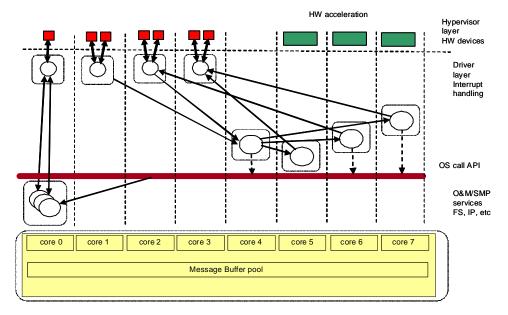

| 5-3              | OSE5 Multicore Output Simulation                                                               | 5-10           |

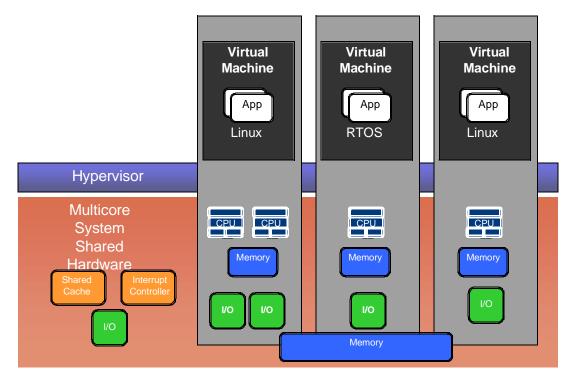

| 6-1              | Relationships among VMs, the Native Hypervisor, and Underlying Hardware on<br>Multicore Device |                |

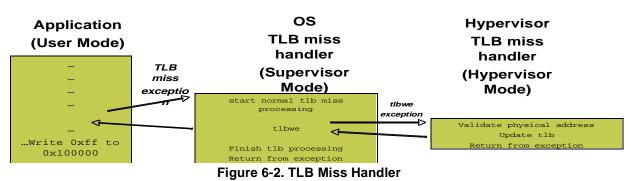

| 6-2              | TLB Miss Handler                                                                               |                |

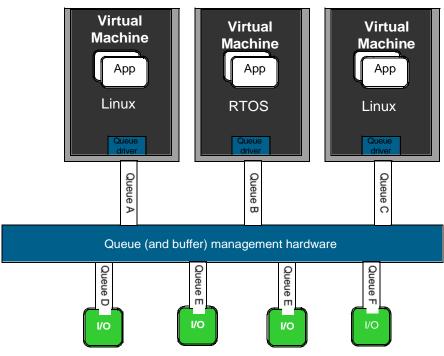

| 6-3              | Abstraction Of Peripherals Using Queues                                                        |                |

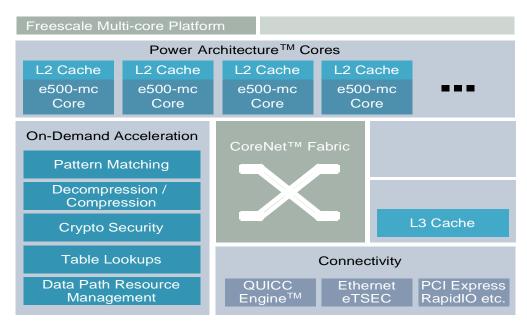

| 6-4              | QorIQ Processor Family                                                                         |                |

| 7-1              | Virtual Platform Running the Same Software as the Physical Hardware                            |                |

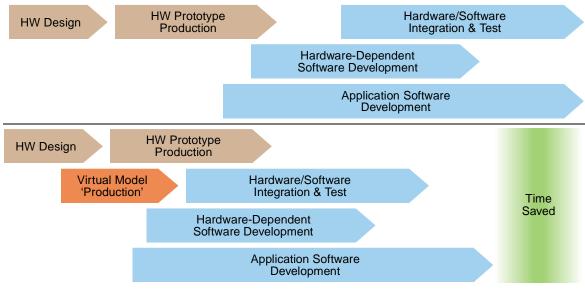

| 7-2              | Virtual Platforms Make the Hardware Available Sooner                                           |                |

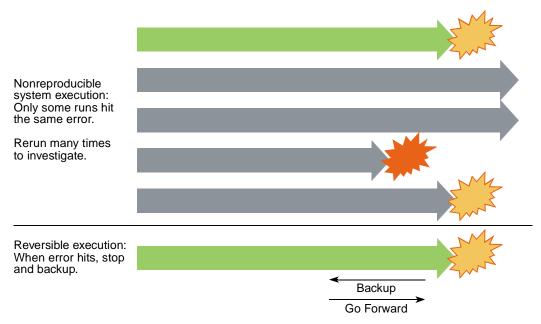

| 7-3              | Reverse Execution                                                                              | 7-5            |

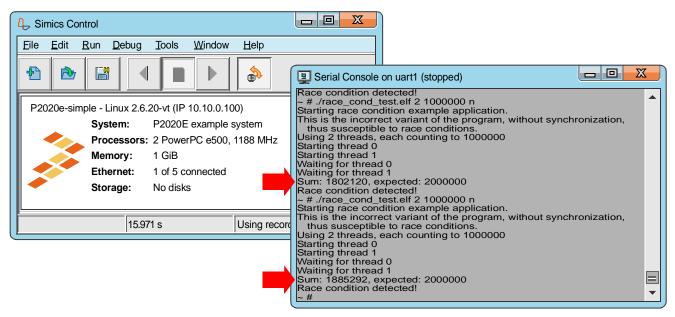

| 7-4              | Example Output from a Multicore Run on a Virtual Platform                                      |                |

## Chapter 1 Embedded Multicore, an Overview

-Jonas Svennebring

The computer industry is driven by pursuit of ever increasing performance. From high-end customized special-purpose computing in networking, telecommunications, and avionics to low-power embedded computing in desktop computing, portable computing and video games, customers expect faster, more efficient, and more powerful products. However, single core products are showing a diminishing ability to increase product performance at pace with consumer desire. Multicore processing is recognized as a key component for continued performance improvements.

The industry is on a clear path towards an increasing number of cores. Dualand quad-core devices have been established for several years, and they are just the beginning of the explosion in the number of cores per device.

However, this kind of expansion creates a challenge, not only for the semiconductor industry, but also for the system and software designers who put them to work. Writing applications that execute in parallel is seldom easy; sometimes it is not even possible. So why is the industry moving this way? What are the problems, and how can we smoothly work around them?

Those questions are answered in the following sections:

- "Section 1.1, "Why Multicore?" provides an overview of the reasons behind a migration to multicore, the difficulties in raising clock frequency further and, as a result, improving performance.

- "Section 1.2, "Different Types of Multicore" describes the basic topologies across the array of computational environments, including homogenous systems where all cores are identical and heterogeneous multicore systems where these cores differ, including the three predominant approaches to memory designs: distributed, shared, and hybrid.

- "Section 1.3, "Parallelism" outlines the difficulties of managing a system with multiple cores running in parallel and describes the four common forms of parallelism: bit level, instruction, data, and task.

- "Section 1.4, "System and Software Design" compares the advantages and disadvantages of the two approaches to multiprocessing:

asymmetric multiprocessing (AMP), in which each core runs standalone, and symmetric multiprocessing (SMP), in which the many cores act as one through the operating system.

Subsequent chapters focus on hardware, software architecture (such as AMP and SMP systems), changes to operating systems and why system simulation will play a more important role in the development process.

## 1.1 Why Multicore?

The migration to multicore devices requires complex changes to system and software to obtain optimal performance. It is reasonable to question whether multicore is worth this additional work, or whether it is possible to continue gaining improvements through single-core devices

Before the advent of multicore, most efforts in improving performance increase were straightforward: Crank up the frequency! But it has become all too apparent that pushing the frequency came at a price. Frequency improvements penalize power consumption, which in turn generates heat that requires more advanced cooling, decreases reliability, and shortens the longevity of the device. So, solving the additional problems that come with increasing frequency costs more money.

A rule of thumb is that doubling the frequency causes a fourfold increase in power consumption. Power consumption itself is only proportional to frequency, but higher frequencies need increased voltage because processors with higher speed transistors leak more than slow ones. Equation 1-1 explains the relationship.

## power = $capacitance \times voltage^2 \times frequency$

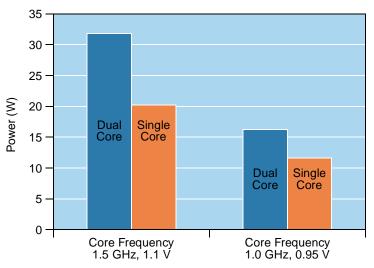

Figure 1-1 compares single- and dual-core implementations of the MPC8641. In a single-core configuration, raising the frequency by 50% roughly doubles power consumption; however, dual-core increases power by only 30%.

Figure 1-1. Improved Power Consumption as an Incentive for Multicore (MPC8641)

Embedded Multicore: An Introduction, Rev. 0

Eqn. 1-1

It is well understood that simply doubling the core frequency does not double performance. Techniques such as parallelizing instructions, speculative execution, and pipelining cannot generally scale with the frequency. For example, some stages in an instruction pipeline have internal timing requirements that cannot be met if the processor clock frequency is increased. Therefore, the instruction latency of many instructions cannot scale proportionately and additional pipeline stages are necessary. This naturally increases the number of cycles required for execution and penalizes branches. Although doubling the core frequency may still allow such instructions to execute faster than they would on a core running at a slower-frequency, lengthening the pipeline means that this improvement is less than double.

Of particular significance is the so-called "memory wall" that has materialized as the increase in the on-core speed is not matched by the speed of off-core and off-chip memory and IO subsystems. A high-frequency core matched with a lower-frequency bus will frequently stall as the core waits for data. To some extent such disparities have been compensated by implementing large, fast, on-chip caches, but increasing the size and numbers of on-chip caches subsequently increases both silicon size and power consumption.

Power conservation is especially critical for embedded systems. In a conventional system implementation, the standard upper ceiling of around 20–40 W requires a heat sink and either a fan or substantial air flow for cooling. Ensuring that hot spots are distributed effectively complicates both board layout and the layout of boards within a larger system. This may be acceptable for high-end devices, but not when power requirements drop below approximately 7 W.

When the core runs at about 7 W, the fan can be removed and there is less need for sophisticated management of hot spots. This, in turn, saves money, simplifies board design, and offers more flexibility for placing high-end processors in computing environments where low power is a critical necessity. There are low-power multicore devices that consume only around 2 W, such as the e300-based MPC5121 with integrated graphics and a signal-processing accelerator. For most applications, these devices can be implemented without a heat sink.

Through a great deal of effort and cost, the performance race for desktop and embedded systems has overcome the issues that arise with increasing the frequency. However, innovative workarounds are coming to an end. To continue delivering higher performance with improved power consumption, a new path must be taken. In fact, that trail has been blazed by ultra-high-end systems, such as supercomputers, in which even tens of thousands of CPUs are increasingly common.

## 1.2 Different Types of Multicore

Given the growing importance of multiprocessing across the computing spectrum and that high-end systems, such as telecom infrastructure, servers, and supercomputers, have long used multiple-core designs as the standard, is natural that the gains of high-end computing be applied to embedded computing systems. These systems have much to offer on how to design and develop software, which is the focus of later chapters.

#### Embedded Multicore, an Overview

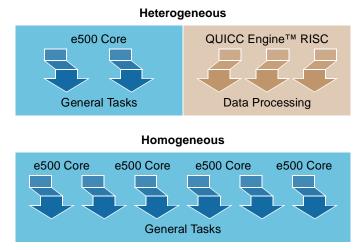

Multicore devices have been around for many years in different forms. For example, Freescale's PowerQUICC<sup>TM</sup> devices implement cores built on Power Architecture<sup>TM</sup> technology, such as the e500 cores used in PowerQUICC III devices and the single or dual RISC cores in the QUICC Engine<sup>TM</sup> communication unit. Figure 1-2 shows the different types of multicore environments. A device that contains multiple cores with different types of instruction sets is referred to as *heterogeneous*. In contrast, *homogeneous* multicore devices implement multiple identical cores, as seen in the MPC8641 and P2020. The current trend is to create homogeneous

#### homogenous

Describes a multicore environment in which cores are identical and execute the same instruction set.

#### heterogeneous

Describes a multicore environment in which cores are not identical and implement different instruction sets

multicore devices, but a significant performance advantage can be obtained by using specialized cores and accelerators to offload the main cores.

Figure 1-2. Heterogeneous and Homogeneous

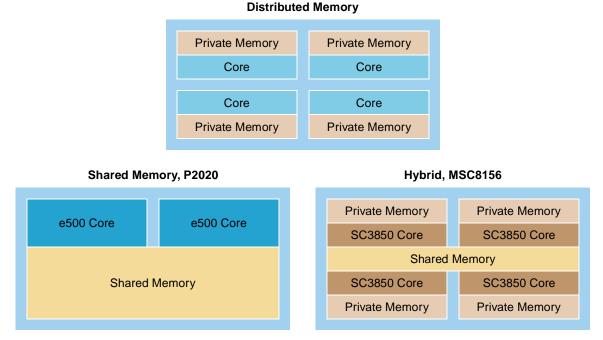

Figure 1-3 shows basic core memory topologies.

- In distributed memory designs, each CPU typically has a private memory and communication between CPUs is performed over a high-speed network

- In a shared memory design, there is a public memory that is shared by multiple cores.

- In a hybrid design, there is a shared memory resource, but each core has private memory as well. This allows each CPU/core to have a private memory that can smoothly be shared on a public memory.

Figure 1-3. Memory Designs in Multiple CPU Systems

As process technology shrinks below 45 nm, devices can be implemented with not just two and four cores, but many tens of cores, an approach commonly referred to as manycore rather than multicore. It is there that the biggest challenges for system and software design lie. A dual-core device can typically provide performance increase without any changes because the operating system can dedicate one core for the main application and the other for special tasks such as interrupt handling. However, in a manycore device applications must be redesigned to make use of all cores to take optimal advantage of the processing power available.

## 1.3 Parallelism

Parallelization is the central challenge of developing a multicore environment. Of course, parallel execution is nothing new. However, implementing a system in which work can be done in parallel in a computing environment in which order must be maintained at all costs poses problems. Why can't this be solved in the hardware, or by the compiler or operating system? The answer is that parallelization has already been implemented in these areas.

Parallelism can be thought of as taking four basic forms—bit level, instruction, data, and task. These forms are discussed in the subsequent sections.

#### 1.3.1 **Bit-Level Parallelism**

Bit-level parallelism extends the hardware architecture to operate simultaneously on larger data. For example, on an 8-bit core, performing computation on a 16-bit data object requires two instructions. However, by extending the word length (the native data length that a core works with) from 8 to 16, the operation can now be executed by a single instruction. Thus as the computer industry has matured, word length has doubled from 4-bit cores through 8-, 16-, 32-, and 64-bit cores.

#### 1.3.2 Instruction-Level Parallelism

Instruction-level parallelism (ILP) is the technique for identifying instructions that do not depend on each other, such as working with different variables and executing them at the same time. Because programs are typically sequential in structure, this is not an easy task. Certain applications, such as signal processing for voice and video, can function efficiently. A DSP, for example, and the Freescale StarCore<sup>TM</sup> architecture can execute 6 instructions per cycle per core or double this rate when working with video processing. ILP is commonly implemented in the compiler. Other common techniques in this area are speculative and out-of-order execution, features supported by the RISC-based Power ISA, and are implemented in the e500 and the legacy PowerPC cores, such as the e300 and e600.

#### **Data Parallelism** 1.3.3

Data parallelism allows multiple units to process the data concurrently. One such technique implemented in hardware is SIMD (single instruction/multiple data), which is implemented in the 128-bit vector instructions defined by the AltiVec instruction set and the 64-bit vector instructions defined by the signal-processing engine (SPE) instruction set.

Data parallelism is also where multicore plays a significant role. Performance improvement depends on many cores being able to work on the data at the same time. When the algorithm is sequential in nature, difficulties arise. Crypto protocols, such as 3DES (triple data encryption standard) and AES (advanced encryption standard), are often sequential and therefore difficult to parallelize whereas matrix operations are generally easier to parallelize because the data is interlinked to a lesser degree. In general, it is not possible to automate data parallelism in hardware or through a compiler because a reliable, robust algorithm is difficult to assemble. Another difficulty is identifying which parts of the software should be parallelized as not all functions benefit from parallel execution. Both of these are problems that you will face when doing it by hand.

#### 1.3.4 **Task Parallelism**

Task parallelism distributes different applications, processes, or *threads* to different units. This can be done either manually or with the help of the operating system. The difficulty with task parallelism is not with how to distribute the threads, but with how to divide the application into multiple threads. For systems with many small units, such as a computer game, this can be easy. However, when

thread

A flow of instructions that runs on a CPU independently from other flows

Embedded Multicore: An Introduction. Rev. 0

there is only one heavy and well-integrated task, this division can be very difficult and often faces the same problems associated with data parallelism.

## 1.4 System and Software Design

Of the four types of parallelism, multicore focuses most on data and task parallelism. Accordingly, this is where the system and software design matters. This section provides a brief overview, different design approaches for handling tasks, and data management in parallel.

The simplest way to progress from single-core to multicore computing is to run each core independently. This approach is called *asymmetric multiprocessing* (AMP or ASMP) in contrast to *symmetric multiprocessing* (SMP), in which all of the cores act as one through the operating system.

In an AMP design, each core runs by itself and often is dedicated to a single task, such as decoding incoming data or handling a specific step in data processing. This can be done in a general-purpose core or in a custom-designed core that has a dedicated security unit for performing encryption and decryption, such as Freescale's P2020.

asymmetric processing (AMP or ASMP)

An approach to multicore design in which cores operate independently and perform dedicated tasks.

symmetric processing (SMP)

An approach to multicore design in which all cores share the same memory, operating systems, and other resources

An AMP system can be designed in which a set of cores can perform all of the tasks required for the complete processing of a particular task so that the same process can be performed on multiple cores running in parallel. Alternatively, a system can be defined in such a way that each core specializes on a single step in a multiple-step process where results are passed like serial stages in a pipeline.

With either AMP approach, it is important that the hardware distributes the work among the cores. In the case of Ethernet traffic, for example, this can be done by filtering MAC or IP addresses to specific cores. However, with an SMP design, the operating system distributes the work. SMP requires homogeneous cores that share memory such that any thread or process can be assigned to any core at any time. Assuming that an application is divided into multiple threads, this is a very convenient approach because the operating system does most of the work. However, there are performance losses because all cores compete for the same memory with SMP. Currently, this memory bottleneck sets a practical upper limit of about eight cores, although there are ideas for how this can be extended further. These ideas are discussed in subsequent chapters.

Combinations of SMP and AMP yield good results in scenarios in which the main system runs on a few cores that use SMP and are helped by cores running AMP modes as software accelerators. For example, in applications such as telecom 3G/LTE, one or more such accelerators process layer 1 and hand off the processed data to layer 2, which is running with SMP. One core may run a real-time OS and the other Linux (see Figure 1-5).

When multiple operating systems run on the same device, they need to share common resources. For memory, the MMU can easily do this, but for interfaces it is more complicated. The general solution to this problem lies a level below the operating system and is called a *hypervisor*. The hypervisor provides system-level resources that allow operating systems to interface. It

#### hypervisor

System-level software that allows multiple operating systems to access common peripherals and memory resources and provides a communication mechanism among the cores.

#### Embedded Multicore, an Overview

is through the hypervisor that operating systems communicate with each other and with the shared hardware.

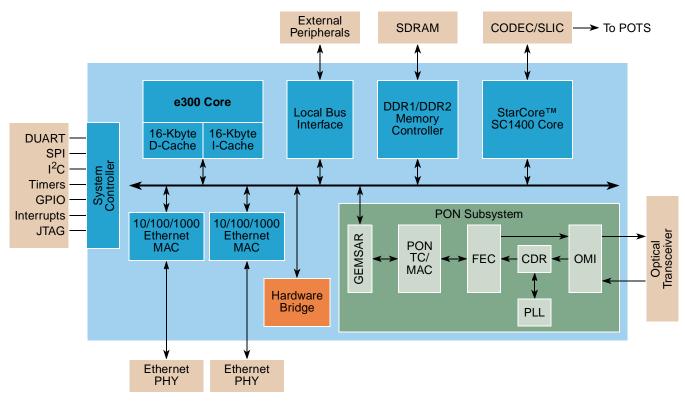

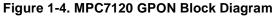

Multilayer systems can benefit from a heterogeneous device with cores dedicated to the specific tasks. Figure 1-4 shows the MSC7120, one such example for GPON (gigabit parallel optical networks, i.e., fiber to the home). It features an accelerator block for the physical layer, a Starcore SC1400 core for signal processing, and an e300 core built on Power Architecture technology for higher layers of processing.

Figure 1-5. Mix and Match

#### Embedded Multicore, an Overview

*Virtualization* is a technique that allows one unit to act as multiple units or vice versa. For the embedded market, virtualization can be used to move a legacy system into a device, such as merging multiple single-core systems into one multicore device.

Full virtualization features a complete simulation of the underlying hardware so that any software that can run on the real hardware can also run on the virtual machine. The drawback to this approach is the performance overhead. *Paravirtualization* can reduce the overhead. In this scenario, the software needs to be aware of the virtualization and therefore has to be ported. For more information about virtualization, see Chapter 6, "Virtualization and the Hypervisor."

## 1.5 Conclusion

Multicore devices provide a path forward for increased performance. This path requires comprehensive and pervasive system and software changes as well as new, innovative hardware designs to ensure that the software can take advantage of the increased computational power. Freescale has years of experience with many types of embedded multicore devices and thus can ensure that all necessary components are present to ease the software burden and to avoid having an inefficient core. This balance is key for multicore applications.

#### virtualization

A computing concept in which an OS runs on a software implementation of a machine, that is, a virtual machine (VM). *paravirtualization*

A virtualization technique that presents a software interface to virtual machines that is similar, but not identical, to that of the underlying hardware.

## Chapter 2 Embedded Multicore from a Hardware Perspective

-Jonas Svennebring

As the computer industry transitions into multicore computing, the hardware must change shape accordingly. The change must happen not only in the number of cores and how the software uses them, but also in the supporting functionality. Memory and communication interfaces (Ethernet/PCI Express®/Serial RapidIO) and accelerators for crypto, deep packet inspection, and communication stacks that have traditionally resided outside the chip are moved onboard for higher integration purposes and to optimize and balance the loads shared by the cores.

This chapter examines the hardware aspects of multicore computing more deeply by looking at two Freescale homogenous multicore device solutions: general-purpose processors (GPP) and digital signal processors (DSP). It contains the following main sections:

- Section 2.1, "Multicore Devices," discusses a representative GPP device and a representative DSP device. It also discusses power savings, system-level stability, and security.

- Section 2.2, "From Coprocessors to Multiple Cores," discusses the evolution of devices to multicore and the attendant technological issues.

Embedded Multicore from a Hardware Perspective

## 2.1 Multicore Devices

We begin by focusing on homogeneous cores: devices that require more re-architecting than a simple addition of cores to the silicon. As examples, we use two Freescale multicore solutions from the two main device groups: general-purpose processors (GPP) and digital signal processors (DSP).

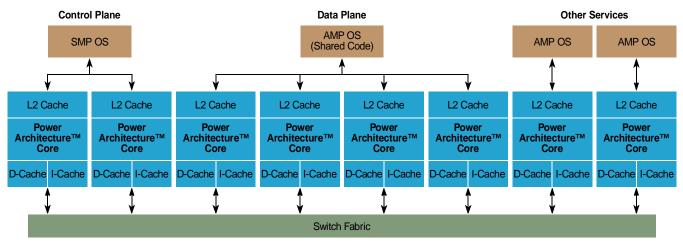

Figure 2-1 shows an example of a GPP: the  $QorIQ^{TM}$  (pronounced like "core IQ") communication processor P4080 based on Power Architecture technology.

Figure 2-1. P4080 Block Diagram

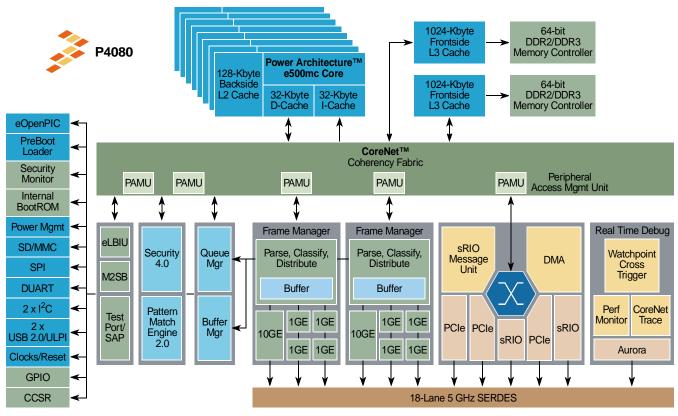

Figure 2-2 shows the MSC8144 Starcore<sup>®</sup> DSP.

Figure 2-2. MSC8144 Block Diagram

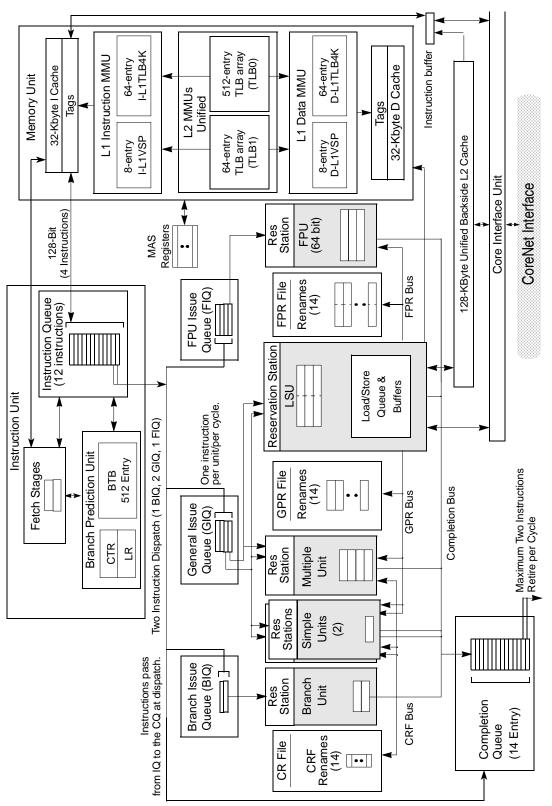

In a homogeneous environment, relatively little in the basic core functionality of instruction execution directly changes. As a reference, Figure 2-3 shows the Freescale e500mc core. Like other cores in the e500 family, the e500mc uses superscalar dispatch, a seven-stage pipeline, and an ability to dispatch and retire two instructions per cycle. The e500mc's five execution units, the branch, floating-point, load/store, and two integer units, allow out-of-order execution to minimize resource and memory stalls and features a completion queue that ensures in-order completion.

Each of the P4080's eight cores run standalone, with the principal goal of having each core run as independently of each other as possible, thus avoiding stalls due to core collisions from attempts to access the same peripherals or memory. This, in combination with high performance and a relatively small die size, makes the e500mc core a good base for multicore devices.

Figure 2-3. e500mc Block Diagram

# Coupling the need to synchronize software on the different cores with the need to minimize the number of wasted cycles makes core-to-core communication a critical priority. Starcore devices employ *virtual interrupts* so that each core can get another's attention quickly. With the e500mc, a

virtual interrupt

Embedded Multicore from a Hardware Perspective

A software-triggered interrupt from one core to another.

similar approach is adopted by the Message Send and Message Clear instructions, **msgsnd** and **msgclr**. These two new instructions, now part of the Power Architecture, are used to allow one core to signal a doorbell interrupt to another.

## 2.1.1 Power Savings

Another goal of hardware design is to maximize the power consumption made possible by migrating to multicore. Devices typically implement modes that halt execution and power down the device to different degrees—for example, nap, doze, and sleep. However these modes can be difficult to enable in the software, and the wake-up can be time consuming, especially if the PLLs (phase-lock loops) require resynchronization. To simplify this, the e500mc core introduces a **wait** [for interrupt] instruction that halts execution on a specific core until an interrupt occurs. While the processor waits, instruction fetching stops, and the execution pipeline idles.

To further reduce power, the P4080 has separate power rails with different voltages, including complete shutdown (static and dynamic) of all or a subset of cores and multiple PLLs to allow some cores to run at lower, less power-consuming clock frequencies.

## 2.1.2 System-Level Stability and Security

In a traditional single-processor, single-operating system environment, there is a need for only two privilege levels, one for the operating system (supervisor) and one for the user applications (user or problem-state). But in a multiple-core, multiple-operating system system, it is necessary to add a layer of privilege to coordinate all of the competing domains within the system. Freescale's instruction set architects have extended the Power ISA (instruction set architecture) to include instructions, registers, interrupts, and memory management resources that this additional executive-level software uses to protect memory resources and to provide a virtual interface to peripheral resources that can be shared across all of the computing domains in multicore devices such as the P4080.

This new layer of architecture creates a new privilege level, the hypervisor level. Hypervisor operation is discussed in detail in Chapter 6, "Virtualization and the Hypervisor."

When comparing devices, one should be careful not to look just at the raw core performance, but at how efficiently the surrounding parts can feed the execution units with data, how system bottlenecks are managed and minimized, and how the load can be distributed among the cores. In the Freescale Power Architecture and StarCore devices, the programmable interrupt controller (PIC) can be used to configure how hardware interrupts are prioritized and how they are directed towards specific cores. For example, Tx (transmit) of a device can go to one core and Rx (receive) can go toward another. Another system design approach is to use a fully symmetric interrupt scheme that will ensure that all cores get triggered by an interrupt.

Embedded Multicore from a Hardware Perspective

## 2.2 From Coprocessors to Multiple Cores

The roots of multicore can be traced to the earliest days of microelectronics and the evolutionary trend for more and more logic to move off the board and onto the same chip as the core. Transistors were combined to form small integrated devices and those devices evolved into processors that were given on-chip caches. The continuous improvements in process technology made it practical to integrate special-purpose functionality, such as interrupt

#### 1989 First Multicore

Freescale's first multicore device, M68302, was launched 1989. It was a heterogeneous devices pairing a 68000 core with the CPM.

controllers and DMA into the processors. The next step was to move high-speed communications, video controllers, and peripheral controllers, such as PCI and Ethernet into the devices, this to lower cost and increase performance. It was only natural to call them Systems on a Chip, or SoCs.

With SoCs evolving into multicore devices the ability to process data increases significantly. Data must be communicated to and from the device at a much higher rate. This in turn raises a need for specific hardware acceleration. The Freescale PowerQUICC processor family handles communication processing, for example routing and prioritizing incoming packages, by microcode executed in the QUICC Engine communication unit. With higher data rates, such as the dual 10-Gigabyte Ethernet interfaces on the P4080, this processing has to be implemented directly in the hardware but with flexible configurations.

Other accelerators commonly seen are for encryption and decryption of various protocols, table lookup, and deep packet inspection. At high data rates, these things are difficult to do in software and can offload the cores for other operations; that is, the cores are offloaded to the accelerators so they can do other tasks.

## 2.2.1 Internal Access

Devices typically use a bus-based approach for internal communication. Buses are simple to design, and they give high throughput with low latency as long as there are few masters that initiate data transfers. This is the case with single-core devices, where typically only the core and some advanced peripherals can function as bus masters.

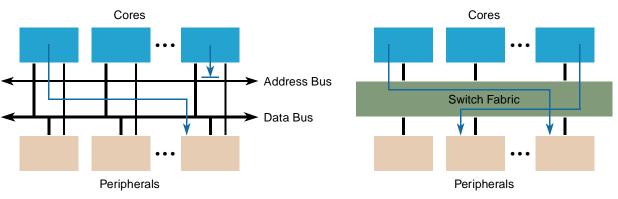

However, the use of buses in multicore devices faces two considerable obstacles: As shown in Figure 2-4, as the number of units increases, so must the physical length of the bus chain. The fixed-signal speed (electron mobility related to the physical properties of the silicon) within the device necessitates an increase in handshake time which in turn limits the clock frequency, reducing bandwidth and increasing latency.

Figure 2-4. Single Bus vs. Switch Fabric

Embedded Multicore: An Introduction, Rev. 0

Ironically, although microprocessors can perform almost instantly the sorts of complex complications that decades ago institutions spent millions on and built rooms for, the step into multicore processing has brought a simple problem to light: Because the total bandwidth must be divided among the bus masters, more cores means less bandwidth per core.

Also, with increased bus traffic, the risk of collisions increases and this lowers bandwidth even further. In short, a bus does not scale well above four cores.

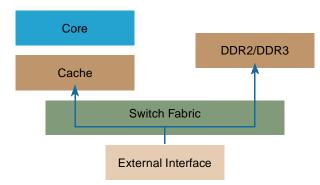

The solution, shown in Figure 2-4, is a *switch fabric*, which allows for multiple simultaneous accesses. With such an approach, as one core communicates with the Serial RapidIO interface, another can access memory, a third can use the Ethernet interface, and so on. The advantages of having dual DDR interfaces can now be fully realized because two sets of cores can work with separate interfaces. To reduce collisions, in addition to on-chip caches, the cores can be spread over the two interfaces. This approach of having multiple access points in the memory can also be seen with the M2 memory on the MSC8144. Because the cores are expected to work directly with the M2 memory, it has four interfaces, one for each core.

#### switch fabric

Interconnect architecture that allows data coming in on one of its ports to be redirected out to another of its ports. All inputs are connected to all possible outputs.

memory layer 2 (M2)

A second-level internal memory, similar to an L2 cache.

The general drawback with switch fabrics is increased latency. Freescale has minimized this, not only to make the fabric itself efficient, but also to pair the cores with nearby cache memory.

Because it is more complex than a bus, there is a desire to optimize a switch fabric, both for the cores that use it and for the applications running on the cores. Freescale uses two different switch fabrics, the CLASS in the Starcore DSPs and CoreNet<sup>TM</sup> technology in the QorIQ communication processors. The software complexity of general-purpose processors increases greatly with multiple cores placed into highly integrated devices, but providing a more sophisticated communication fabric, such as CoreNet, reduces that additional demand on software. To accomplish this, the CoreNet fabric also supports software semaphores by extending the bit-test to guarantee atomic access between cores. The CLASS is better suited for DSPs as they tend to use less complex operating systems and the application software is more in control. For example, after using a software cache coherency, the switch fabric complexity can be reduced and silicon area can be saved.

In a multitasking system, in addition to translating the effective addresses used in software to the physical addresses used by the memory subsystem, a memory management unit (MMU) must protect applications from interfering with each other. Although the MMU provides protection for each core in a multicore system, other masters, such as peripheral DMAs, can corrupt the

memory. Unlike with single-core devices, a multicore system often uses many operating systems which opens the risk of incorrectly configuring other masters so that memory accesses interfere with one another. To prevent this, a new concept of peripheral access management units (PAMU) is introduced into QorIQ devices. Much like an MMU, the PAMU is located at the connection of non-core masters and the CoreNet fabric, as seen in Figure 2-1. The PAMU can be configured to map memory and to limit access windows thereby increasing system stability.

peripheral access management unit (PAMU)

Similar to an MMU, a PAMU is located at the connection of non-core masters and the CoreNet fabric

Embedded Multicore from a Hardware Perspective

## 2.2.2 Memory Hierarchy

The advancement of multicore implementations has been facilitated greatly by continued improvements in process technology. With the introduction of 45-nm technology, core logic forms a relatively small part of the device. In addition, caches are very costly, both in terms of power consumption and size. As the core-to-memory interfaces speed differential increases, it is necessary to increase cache size. As core frequency stabilizes and as caches are shared among cores more efficiently, the demand for cache resources has been reduced.

Looking again at Figure 2-1, we can see that each core has its own Harvard L1 caches, one for data and one for instructions. The caches are very fast and the core can work directly with them by using the core pipeline for prefetch and write-back queues. The unified L2 caches are private to the core but are shared between data and instructions. Medium-sized private caches reduce the risk of resource competition, reducing wasteful cache thrashing between the cores, and give a minimum guaranteed storage area for each core. In other instances, where the core is configured as a software accelerator, the L1 and L2 caches can accommodate all code with plenty of room for data. One can also configure, on a per way basis, the cache as SRAM and address it as normal, store variables, etc.

Backside caches, as in this implementation, are considerably faster than front-side caches and fit well as fast private caches. To maximize usage and minimize core stalls, one can use a feature called cache stashing. Data received from the interfaces are placed in memory and the core is then informed through an interrupt. As the core retrieves the data from memory it instantly suffers from memory stalls since the data has to be transferred from external memory which can be on the order of hundreds of core cycles. However, by using stashing, as seen in Figure 2-5, the data is placed in L1/L2 cache at the same time as it is sent to memory. When the interrupt is triggered the data is conveniently available and the core is fully utilized.

Figure 2-5. Cache Stashing

For most applications, one large code base is either shared by all cores or, if some cores are specialized and running their code in the L1 and L2 caches, is used by a controlling subset of these cores to run this code. Commonly, this type of code is executed randomly with areas of more intense execution. For example, a complex computation or frequently occurring code such as the operating system kernel. The intense and frequent parts will end up in the L2 caches. Having a large, shared L3 cache also captures the less-used parts of the code, which also comprises the largest part of the code footprint. On the P4080 this cache is in line, with the two DDR2/3 memory interfaces.

## 2.2.3 Interfaces

With architectures built for strong computational performance and data throughput, only one piece of the solution remains—external interfaces to pump the huge volumes of incoming and outgoing data. Freescale's approach has been to go with a high degree of integration of common devices. Both the Power Architecture and Starcore devices can be seen with high-speed interfaces, such as Gigabit Ethernet, Serial RapidIO, PCI Express and general buses. Common low- and medium-speed interfaces, such as UART, SPI, I<sup>2</sup>C and USB, are handled easily by any core, but for the enormous flow of data associated with 10-Gb Ethernet interfaces, the work must be divided up between the cores.

With the QorIQ family, Freescale introduces the concept of hardware off-loading through the frame, queue, and buffer managers, shown in Figure 2-1. The frame manager is the central part that connects directly with the Ethernet interfaces. Packets are then brought into a parser and classifier unit that inspects the packet headers, including higher layer protocols up to L4, both standard and user defined as well as user tunneled. Based on pre-configured settings the packets are then sent to different queues, forwarded for decryption, sent out on a different interface, thrown away etc. This is all done at line rate even with a load above 10 Gbps per frame manager. For example, we may decide to assign each core a unique IP address but have all TCP packets to port 80 (HTTP) and port 22 (secure shell) sent to core 0. All UDP packets spread evenly between cores 4-7 and ARP traffic to core 1. As the data gets classified and divided up, the buffer and queue managers (Bman and Qman) take over. Because the buffers are already handled by the hardware, this concept changes and simplifies the way that the drivers in an operating system work. The focus can instead shift to data-path configuration.

## 2.2.4 Debugging and Profiling

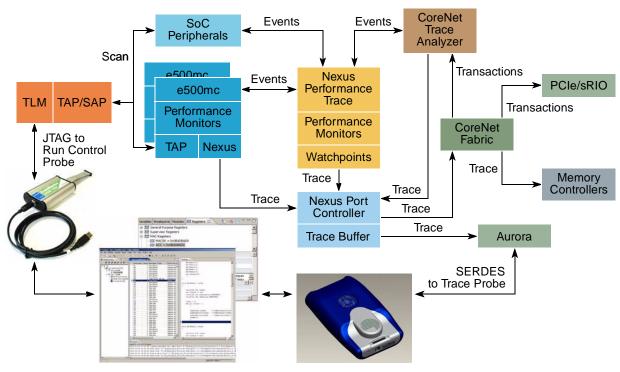

With ever-increasing system complexity, the demand for deeper insight into what happens in the chip is needed to find bugs and optimize performance through profiling. Freescale high-end DSPs and GPPs have long had JTAG-based interfaces to support run-time control and debugging as well as for reading out trace buffers and profiling counters to see how the program executed, what took time, how many cycles were wasted on stalls, and what the reason was. Although this is slightly intrusive, this data can also be read out by running software and operating systems, thereby allowing for transmission over standard high-speed interfaces.

The on-chip debug functionality is now expanded to allow for insight into the switch fabric, data managers, and core interaction. The P4080 has, along with the JTAG connector, also a Nexus port directly to memory or over an Aurora interface. This interface has Gigabit bandwidth and can be used to send not only information on program execution but also information on what data is processed. With a powerful external acquisition unit this data can be recorded and as bugs appear, the user one can go through the execution history and identify the root cause. Figure 2-6 depicts the possibilities and shows both the JTAG

#### Embedded Multicore from a Hardware Perspective

emulator as well as the trace probe. These in turn interface with the CodeWarrior<sup>®</sup> development tools on an ordinary PC.

Figure 2-6. Debug Interface

## 2.3 Conclusion

The transition to multicore devices involves much more than simply adding cores. The glue between the cores has to change from a bus architecture to switch fabrics that allow many to many parallel connections. New approaches to core designs, such as Freescale's cores based on SC3400 Starcore and e500 cores, are needed that adjust for those changes, and those adjustments are facilitated by modern and flexible architectures the provide new functionality that simplifies core-to-core communications. One key problems is how to divide the incoming data among the cores, especially with the high-bandwidth interfaces. One possible solution is the introduction of hardware managers. Hardware and software are being codeveloped to address the new challenges and to leverage the many new possibilities, that will advance overall computational performance.

## Chapter 3 Embedded Multicore: Software Design

-John Logan and Jonas Svennebring

Designing software for embedded multicore devices raises new questions compared to designing for a single-core processor. How do I partition the tasks in my application to achieve the most from the hardware? Should I choose an SMP or AMP software architecture? Which communication and synchronization issues should I consider between tasks?

This chapter explores software design and asymmetric multiprocessing. It includes the following sections:

- Section 3.1, "Amdahl's Law," and Section 3.2, "Gustafson's Law," examine the two concepts that are useful for evaluating parallel algorithms—Amdahl's Law and Gustafson's Law.

- Section 3.3, "Parallelism," examines task and data parallelism.

- Section 3.4, "Symmetric and Asymmetric Multiprocessing," introduces the concepts of symmetric and asymmetric multiprocessing, which are discussed in greater detail in Chapter 4, "Embedded Multicore: SMP and Multithreading."

- Section 3.5, "Processes and Threads," discusses the use of processes, threads, and locks in embedded multicore systems.

## 3.1 Amdahl's Law

The basic aim of a multicore processor is to increase application performance by allowing multiple tasks to run in parallel. This can involve running multiple independent tasks in parallel, multithreading one application so that it runs across multiple cores, or some mixture of both.

For a typical application, there is a portion that cannot be parallelized (called the serial portion) and a portion that can. Ideally, the serial portion is very small. In the 1960s, a computer architect at IBM named Gene Amdahl formulated the equation shown in Equation 3-1, which is referred to as Amdahl's Law. This equation is used to predict the maximum speedup that can be expected in a typical application.

Speedup = 1/(S + (1 - S)/N)Where: *S* is the portion of algorithm running serialized code *N* is the number of processors running parallelized code

Amdahl's Law

#### Eqn. 3-1

For example, consider an image-processing algorithm running on a four-core device (N = 4). Sixty percent of the application can be parallelized across all four cores, and 40% (S = 4) cannot be. With N = 4 and S = 0.4, the expected speedup is as shown in Equation 3-2

Speedup = (1/(0.4 + (1 - 0.4)/(4))) = 1.82

#### Example Speedup for a 60% Parallelizable Application in a Four-Core System Eqn. 3-2

An algorithm that took 10 seconds, now completes in 5.49 seconds.

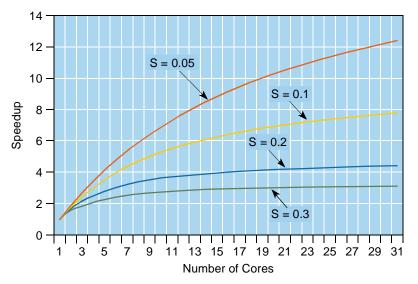

According to Amdahl's Law, the maximum possible speedup is limited by the proportion of the serial portion (*S*) of the application. As more processors are added to the parallelized portion (that is, as N increases), the rate of speedup decreases. See Figure 3-1, which shows curves for Amdahl's Law with varying number of cores and varying sizes of serial portion. As more cores are added, the speedup tends towards 1/S, as shown in Figure 3-1.

Figure 3-1. Amdahl's Law: Speedup as a Function of Number of Cores

Embedded Multicore: An Introduction, Rev. 0

Amdahl's law seems to impose a fundamental limit on the performance boost achievable with multicore processing; however it makes a fundamental assumption about the application. Amdahl's Law assumes the problem size is fixed, that is, the ratio between the serial and parallel portions does not change. For example, in our image-processing example, this would mean you process only a fixed size or number of images. Otherwise, the complete algorithm (serial portion + parallelized portion) must be rerun on each run. In many applications, a fixed problem size model is not appropriate.

## 3.2 Gustafson's Law

There are many examples of applications that do not have a fixed problem size. For example, in a network routing application, there may be an initial configuration phase that cannot be parallelized, followed by the main task of routing and processing data packets. The number of packets is usually unknown; indeed the design goal may be to handle as many packets as possible. In such a system, it's easy to see how adding more cores could boost performance—each core can receive a new packet to process when it has completed processing the last packet. Adding more cores means more packets processed in parallel.

In such a system, the relative size of the serial portion decreases over time and the parallelized portion grows. Gustafson's Law, named after John L. Gustafson, states that the speedup for such a system—known as *scaled speedup*—is as follows:

Scaledspeedup =  $N + (1 - N) \times S$ Where: *S* is the serial portion of algorithm running parallelized *N* is the number of processors

#### Gustafson's Law

#### Eqn. 3-3

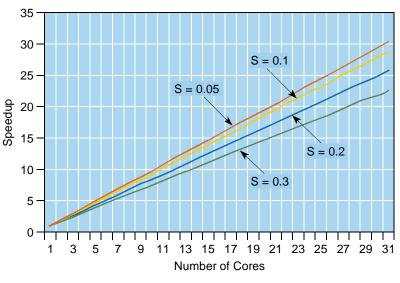

Gustafson's Law shows that for a system where the problem size is not fixed, performance increases can continue to grow by adding more processors. Figure 3-2 shows curves for Gustafson's Law with different values for the serial portion and number of processors. Notice how speed continues to increase with more cores.

Figure 3-2. Gustafson's Law

#### Embedded Multicore: An Introduction, Rev. 0

## 3.3 Parallelism

We now have some simple formulae for evaluating the effects of running an application on a multicore processor. Let's look at different types of parallelism and how an application can be spread across multiple cores.

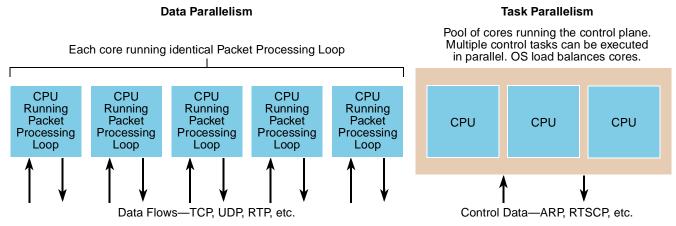

- Task parallelism occurs when each core executes a different task. For example, imagine a word processor application. It can run multiple tasks in parallel on the same data file, such as updating the display, spooling information to a printer, or performing a word count.

- Data parallelism occurs when multiple cores execute the same task on different data sets, such as running the same algorithm on different sections of an array or running the same algorithm on different data packets.

For example, consider an IP-network router application that receives data packets on a number of network interfaces and that must route the data from the correct ingress port to the correct egress port. The router receives IP packets containing different types of data flows. It needs to identify each data flow type, apply the appropriate processing and route the flow to the correct destination. An algorithm could be written to perform this task. An instance of this algorithm could be run on multiple cores of a multicore device to allow it to handle multiple data flows in parallel. This would be an example of data parallelism.

In addition to handling packets for the data flows, which compose the data plane of the router, the router application must also handle control and configuration tasks, which compose the control plane. The control plane contains a diverse range of tasks, such as routing table updates, making statistical measurements, and handling error conditions. Therefore, it needs to run different tasks in parallel—task parallelism.

The high-level block diagram in Figure 3-3 illustrates how the router application can be implemented on an 8-core device, such as the Freescale QorIQ<sup>TM</sup> P4080 family of communication platforms, with data path and control path spread across the cores.

Figure 3-3. Block Diagram of Router Application

## 3.4 Symmetric and Asymmetric Multiprocessing

Multiprocessing has historically been designed for heterogeneous devices such as math, audio, graphics, or communication co-processors. The latter has been very successful for Freescale due to the devices based

on QUICC Engine<sup>™</sup> technology. This type of multiprocessing is called asymmetric (AMP or ASMP) because the cores are different or have different system views and hence cannot share the burden of one task between them.

Due to the inability to increase core frequency, multiprocessing has recently been used to increase the computational performance of the device itself, which requires devices with multiple identical cores. By having identical, equal powered cores with full access to the memory we get a symmetric hardware. Symmetric multiprocessing (SMP) has many advantages for simplifying software design. We will explore these advantages in Chapter 4, "Embedded Multicore: SMP and Multithreading." Although symmetric hardware allows for SMP software, it does not have to be used that way. Each core could be dedicated for a specific task just as easily. For example, one core could have industrial control with real-time functionality, and the other could have user interaction.

The next chapter will focus on SMP software design and operating system functionality.

## 3.5 Processes and Threads

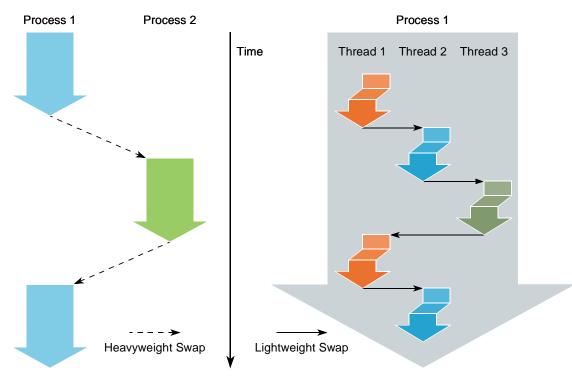

Processes and threads are the two mechanisms that allow an operating system (OS) to provide parallel processing. The term 'process' describes an instance of a program being executed. It has an associated address space and a process control block, which contains attributes and state information about the process.

thread

A flow of instructions running on a CPU independently from other flows

Each process contains one or more threads of execution, or threads. A thread is a basic unit of program execution consisting of a flow of instructions that run on a CPU independently from other flows. Threads within a process share the address space and resources. An SMP operating system schedules threads for execution on the available cores on a device. On a single-core device, threads are time-sliced to give the illusion of multiple tasks running simultaneously. On a multicore device, threads can be truly run in parallel.

For an operating system, switching between processes is a relatively heavyweight task. Typically, context and state information has to be saved for the old process and loaded for the new one, and changes must be made to memory mapping. Swapping between threads in a process is a more lightweight task because the

address space and resources are common. Figure 3-4 shows the relationship between processes and threads.

Figure 3-4. Processes and Threads

To illustrate the difference between processes and threads, we conducted a test on a Freescale MPC8548 running Linux 2.6.23 in which we looped a create and destroy cycle 500,000 times. As a process, this took 115.82 seconds, but as a thread, it took only 40.81 seconds. These results are architecture dependent, but the comparison roughly characterizes the complexity differences between a process and a thread.

## 3.5.1 Task and Process Mapping

In a desktop PC, the operating system takes care of scheduling and running processes and threads. Most desktops run using an SMP operating system—one OS running across all cores—where processes or threads can be mapped to any core. In most cases, the operating system attempts to run threads on the same cores each time they execute. This boosts performance when caches are already loaded with the required data from previous runs.

This linking of threads to specific cores is called processor affinity. Processor *processor affinity* affinity has two forms: soft affinity and hard affinity. Soft affinity exists when the OS prefers to link a process/thread to a specific core, but can choose another if needed. Hard affinity exists when the user/programmer specifies exactly where the process/thread should run. The OS also performs load balancing—spreading the required tasks across cores to minimize waiting.

In an embedded application, it may not be desirable for an OS to completely control mapping of the tasks using soft affinity. Returning to the IP router application example, there are two classes of tasks to be done: data plane and control plane. Data plane tasks handle packets and data flow, such as VOIP, video streams, and network gaming. These typically require low latency, and the system designer must guarantee some Quality of Service or throughput figures for the design. If the data path can be mapped to a specific subset of cores using hard affinity, it is much easier to design and test for these requirements. The control plane is less sensitive to latency and has a large mix

Modification of the native central queue scheduling algorithm. Each queued task has a tag indicating its preferred/kin processor. At allocation time, each task is allocated to its kin processor in preference to others.

soft (or natural) affinity

The tendency of a scheduler to keep processes on the same CPU as long as possible

#### hard affinity

Provided by a system call. Processes must adhere to a specified hard affinity. A processor bound to a particular CPU can run only on that CPU.

of different tasks. It is desirable to map these tasks to another subset of cores and allow the OS to schedule them as appropriate.

Within these two subsets, users may wish to further constrain tasks to particular cores. For example, on the data plane, it may be possible to have one task per core running a very fast algorithm to process data flows. If each task has a single thread, the OS scheduling overhead would be removed. Indeed, if this were possible, it could be possible to run the parallel data plane algorithms without a full OS.

#### 3.5.2 **Run to Completion**

In the early days of computing, users used polling to check for events such as received data on the serial port and key presses on the keyboard. However, for applications with many such possible events, checks with nothing to report wasted time. Moreover, if the event was a burst of data, the first data could have been overwritten by data arriving later by the time polling detected the event.

To address this, interrupts were introduced. Just as it sounds, interrupts permit the event to interrupt the core, which responds by handling the condition associated with the event. When finished handling the interrupt, the core returns to its previous work. The advantages to interrupts are many, but disadvantages also arise when there are large numbers of incoming interrupts. Interrupts have an overhead latency required of jumping to and from the event with registers, stack, privilege level etc., to be shifted out when the interrupt is called for and back in again when it returns. Hence the interrupts are taking core cycles away from the regular applications.

Multiple cores have the flexibility to allocate interrupts among themselves. As described in Chapter 5, "Embedded Multicore: SMP Operating Systems," users can clear out a core and use it only to batch-process data. This principle of run to completion is similar to polling, but in this case, other cores use interrupts to handle events. Polling for more data is only required after a set is processed.

Such an approach yields higher core utilization and also less complex software as it can run with a very limited OS or even on bare metal. Freescale refers to this as an LWE (lightweight executive) and supports it with a rich set of library functions. The LWE contains standard functionality, such as memory management, as well as device drivers and protocols to interact with operating systems running on the other cores.

## 3.5.3 Interprocess Communication and Synchronization

In a system with multiple threads and processes, some communication between processes is needed to pass information or status. Most operating systems provide a set of functions to allow inter process communications (IPC) and to enforce synchronization. Pipes, sockets, message queues, and signals are common constructs used to provide communication. This

document does not look at communication mechanisms in detail; OS documentation should contain full details of the resources it provides.

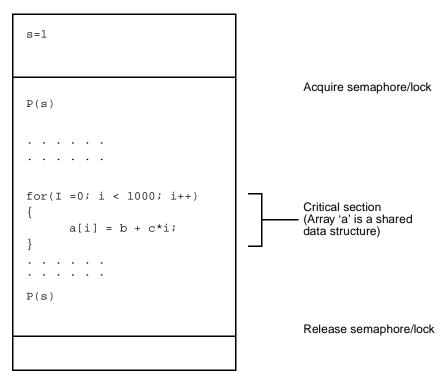

Synchronization is required between threads to prevent them from working on the same data or on shared resources at the same time, which causes data corruption. This can be achieved by adding functions to protect the application's critical sections, which are the sections of code that manipulate shared data. Most operating systems allow a range of synchronization functions based on two types—semaphores and mutex (mutually exclusive) locks.

## 3.5.4 Semaphores and Locks

A semaphore allows or blocks access to a section of code. It consists of two operations—a test function and an increment function—which use an integer variable. As shown in Example 3-1, there are two functions: P (*proeberen*, test) and V (*verhogen*, increment). Both operate on the semaphore variable *s*.

## Example 3-1. Semaphores

```

P(s)

{

s = s-1; /*This must be an atomic operation*/

wait until s >= 0 {}

}

V(s)

{

s = s+1; /* This must be an atomic operation */

}

```

Imagine a scenario where A and B are two threads that engage in the following sequence of actions.

- 1. Thread A and Thread B try to access the same critical section of code; s is initially set to 1.

- 2. Thread A enters P function and decrements s (s = 0).

- 3. Thread A can continue to execute the critical section. Meanwhile, Thread B also enters P and decrements s (s now = -1). Thread B must wait while s is less than 0.

- 4. Thread A runs the critical section and enters the V function, incrementing s to 0.

#### Embedded Multicore: An Introduction, Rev. 0

#### bare metal

Bare metal (or bare board) is application software running directly on the hardware, i.e. running without an underlying operating system.

pipes

Software connections between programs. e.g., in Linux command line "Is \*.c > grep main"

proeberen and verhogen

Proeberen is Dutch for 'Try', Verhogen is Dutch for 'Increment'—so named by Edsger Dijkstra, the Dutch computer scientist who defined the functions.

- 5. Thread B can stop waiting and execute the critical section.

- 6. Thread B finishes and runs the V function, incrementing s (s = 1).

The increment and decrement functions can be implemented in software, but are commonly implemented with a special bit test and set atomic instruction to ensure that there is no task switch between test and set. In Freescale's QorIQ family, the CoreNet switch fabric also has functionality that ensures exclusive access between the cores such that only one core has access to the lock-bit at any given cycle. The Starcore family can do similar operations with cache configurations; they also have special hardware semaphores. Such techniques simplify software design.

In the above example, a thread waiting for the semaphore prevents a core from executing any other code; the core sits in a loop waiting. Most operating systems add wait queues to prevent this from happening. When a thread is waiting for a semaphore, it is put on a wait queue. The OS can then schedule another thread to run on the core. When the semaphore become available ( $\mathbf{s} > 0$ ), the thread is taken off the wait queue and can resume operation. Semaphores can have values greater than 1, allowing more than one thread to share the resource at the same time. This is also useful for sharing resources that can support multiple clients.

Figure 3-5 depicts a critical section of code containing a shared data structure, in this case array a[].

## Program Code

Figure 3-5. Using Semaphores to Protect a Critical Section

Mutex locks, or locks, are similar to semaphores, but a lock can only allow one thread access to a critical section. Typically, a lock has acquire and release functions. Chapter 4, "Embedded Multicore: SMP and Multithreading," addresses this topic further, explaining common issues and how to optimize lock usage.

## Conclusion

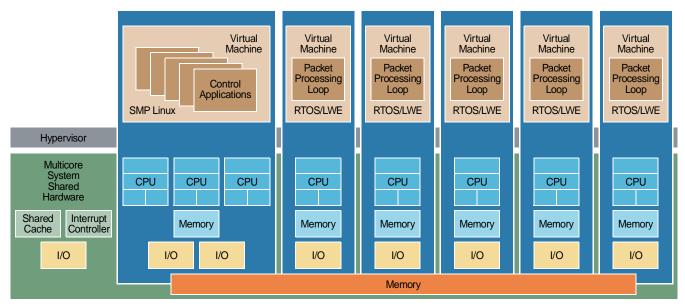

At this stage, we have some ideas about how to partition a system. Figure 3-6 shows a block diagram of the application partitioning, providing an example of implementation on a real machine. The control plane processing is done in a single SMP configuration running, for example, Linux. The data plane is implemented using cores running AMP mode with an identical packet processing loop. Each of these could run an RTOS (real-time operating system) such as Enea's OSE® or as an LWE. Within each of the two planes—data and control—there is room to further parallelize specific parts of each task's algorithm. Tools such as Amdahl's and Gustafson's laws can be used to estimate the performance with particular algorithms, allowing one to make a judgement on the best solution.

Figure 3-6. Network Routing Application

## Chapter 4 Embedded Multicore: SMP and Multithreading

—Jonas Svennebring

As discussed in the previous chapters, multicore processing overcomes many barriers found in single-core computing, particularly in terms of performance and power management. Symmetric multiprocessing (SMP) simplifies the changes required to reap the full benefits of migrating to multicore. However, in order for the operating system to balance an application over the cores, software must be retooled to take advantage of parallelization.

This chapter describes different techniques for parallelization and explains how to implement them. It includes the following sections:

- Section 4.1, "Introduction to Symmetric Multiprocessing," summarizes advantages and disadvantages of symmetric multiprocessing.

- Section 4.2, "Parallelized Application Designs," describes the three primary design approaches to parallelization: master/worker, peer, and pipeline.

- Section 4.3, "Macro- and Microparallelization," describes different levels of parallelization and the support provided by the POSIX and OpenMP multiprocessing standards.

- Section 4.4, "Performance Constraints and Common Pitfalls," describes special concerns for working in a multiprocessor environment, and how to address them through the use of various locking strategies.

# 4.1 Introduction to Symmetric Multiprocessing

Symmetric multiprocessing (SMP) is a system with multiple processors or a device with multiple integrated cores in which all computational units share the same memory. This chapter focuses on the latter. With the support of an SMP-aware operating system, each core can be load-balanced to ensure that the workload is evenly distributed across the system for maximum overall performance. Because the memory is shared, any core can handle any task at any time. The operating system scheduler assigns a task for each core rather than selecting one task at a time to run system wide.

An advantage of SMP systems is their relative ease of implementation; they work similarly to a single-core system, but with maximum performance proportionate to the number of cores, as described by Section 3.2, "Gustafson's Law." The focus shifts to the application and how to partition it into different tasks, as is described in the following sections.

The disadvantage of SMP is scalability. Commonly, 8 to 16 computational units are believed to be the maximum number of cores that improve performance. This is due in part to Section 3.1, "Amdahl's Law," which shows that even a small amount of sequential code reduces scalability. It is therefore important that the operating system functionality allows a high degree of parallelization and that system calls from one task do not stall another. On the hardware side, the memory structure also limits scaling of SMP. Because each core needs to access the shared memory, increasing the number of cores increases the number of access stalls.

Both of these limitations can be addressed as the number of cores on devices approaches the scaling limit. With respect to software, the kernel and libraries can be reworked to better allow multiple simultaneous calls, limit semaphore locking, or other needs. The hardware architectures can replace the bus connection with more scalable switch fabrics, multiple memory interfaces, and advanced hardware coherent caches, as described in Chapter 2, "Embedded Multicore from a Hardware Perspective."

Another solution is to break the SMP guideline of attaching all cores to a common shared memory. A nonuniform memory architecture (NUMA) provides separate memory resources that are only available to a single core or subset of cores. Then, through a slower connection, one group of cores can access the other group's memory and the scaling can continue. However, NUMA complicates task scheduling for the operating system because a particular task cannot be scheduled freely to any other core at any time without incurring an initial penalty in transferring the data to a different memory block. To some degree this extra complexity is already there, inasmuch as cache usage gives a penalty if tasks are transferred between cores. Most SMP systems have processor affinity awareness and take the hardware design into account when scheduling. Chapter 5, "Embedded Multicore: SMP Operating Systems," discusses this in the context of Linux.

For future SMP development, device performance is not simply a multiplication of the number of cores by their individual raw performance. True performance with multicore devices is not equal to number of cores times their performance. Freescale is pushing for fewer but stronger cores, rather than taking the approach of competitors who have many weak cores, which in the end, results in poorer performance because of the inability to scale well. If the surrounding software support and hardware glue is not good enough, the outcome could be very low system performance.

#### 4.2 **Parallelized Application Designs**

A parallelized application typically has one of the following designs:

| 1 11          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |