POLITECNICO DI MILANO Dipartimento di Elettronica e Informazione Dottorato di Ricerca in Ingegneria dell'Informazione

## Cross-Layer Frameworks for Constrained Power and Resources Management of Embedded Systems

Doctoral Dissertation of **Patrick BELLASI**

Advisor Prof. William FORNACIARI

Tutor Prof.ssa Letizia TANCA

Supervisor of the Doctoral Program: **Prof. Patrizio COLANERI**

2009 — XXII

This document was sent to the publisher on January 25th, 2010.

The author can be reached for comments, questions and suggestions at the following e-mail address: derkling@gmail.com.

Copyright © 2009 by Patrick Bellasi. All rights reserved. You may copy and distribute exact replicas of this document as you receive it, in any medium, provided that you keep intact all the contents, including this copyright notice. You may at your option charge a fee for the media and/or handling involved in creating a unique copy of this document for use offline. You may not charge a fee for the document itself. You may not charge a fee for the sole service of providing access to and/or use of the contents via a network (e.g. the Internet), whether it be via the world wide web, FTP, or any other method.

to all my dears

# Contents

#### Abstract

| 1 | Ove      | Verview 5 |                                                           |    |  |  |

|---|----------|-----------|-----------------------------------------------------------|----|--|--|

|   | 1.1      | Design    | ning embedded systems is getting more and more difficult  | 5  |  |  |

|   | 1.2      | Requi     | rement for Power and Performances optimization techniques | 12 |  |  |

|   | 1.3      | Why w     | we focus on Linux                                         | 14 |  |  |

|   | 1.4      | Many      | techniques are possible, just one is chosen               | 16 |  |  |

|   | 1.5      | The fu    | undamental approach of this thesis                        | 19 |  |  |

|   | 1.6      |           | nal objective of this thesis                              | 22 |  |  |

|   | 1.7      | A bird    | d-eye-view on the proposed technique                      | 22 |  |  |

|   | 1.8      | Advar     | ntages of this approach                                   | 25 |  |  |

|   | 1.9      | Frequ     | ently raised objections                                   | 27 |  |  |

|   |          | 1.9.1     | «Your novel contribution is not quite clear»              | 28 |  |  |

|   |          | 1.9.2     | «CPM has already been implemented!»                       | 28 |  |  |

|   |          | 1.9.3     | «Your approach is too limited»                            | 28 |  |  |

|   |          | 1.9.4     | «Your approach is too difficult to actually use it»       | 29 |  |  |

|   | 1.10     | The or    | rganization of this thesis                                | 29 |  |  |

| 2 | Bacl     | kgroun    | d                                                         | 31 |  |  |

| - | 2.1      | 0         | ing Power Consumption                                     | 33 |  |  |

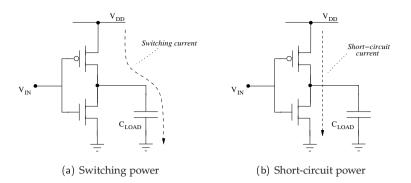

|   |          | 2.1.1     | Dynamic Power Consumption                                 | 33 |  |  |

|   |          | 2.1.2     | Static Power Consumption                                  | 35 |  |  |

|   |          | 2.1.3     | Some Observations on Power Reduction                      | 37 |  |  |

|   | 2.2      | 9         | to Reduce Power Consumptions?                             | 37 |  |  |

|   |          | 2.2.1     | Clock Gating                                              | 37 |  |  |

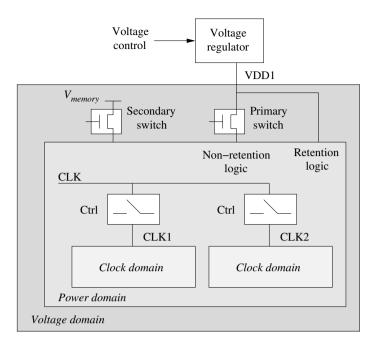

|   |          | 2.2.2     | Multi Voltage                                             | 39 |  |  |

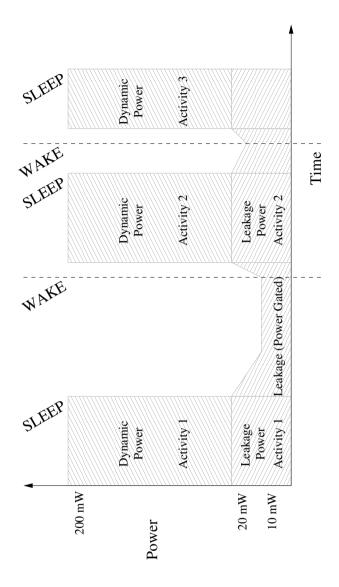

|   |          | 2.2.3     | Power Gating                                              | 43 |  |  |

|   |          | 2.2.4     | Resources hibernation (DPM)                               | 46 |  |  |

|   |          | 2.2.5     | Resources tuning (DVFS)                                   | 47 |  |  |

|   |          | 2.2.6     | Compiler based optimizations                              | 49 |  |  |

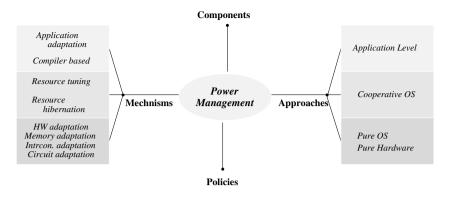

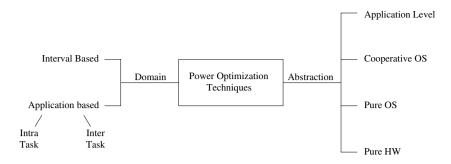

|   | 2.3      |           | Art Techniques                                            | 50 |  |  |

|   | <i>_</i> |           | L                                                         | 2  |  |  |

|   |      | 2.3.1  | Pure Hardware Techniques                       |

|---|------|--------|------------------------------------------------|

|   |      | 2.3.2  | Pure OS-Based Techniques 53                    |

|   |      | 2.3.3  | Cooperative-OS Techniques                      |

|   |      | 2.3.4  | Application-Level Techniques                   |

|   |      | 2.3.5  | Cross-Layer Techniques                         |

|   |      | _      |                                                |

| 3 |      |        | e of the Technique 61                          |

|   | 3.1  |        | ing the Reality                                |

|   | 3.2  |        | acting the Reality, Modeling the Abstraction   |

|   | 3.3  | From   | Reality to the Abstract Layer                  |

|   |      | 3.3.1  | Resources Abstraction                          |

|   |      | 3.3.2  | Architecture Abstraction                       |

|   |      | 3.3.3  | Devices Abstraction                            |

|   | 3.4  | The M  | Iodel Layer         75                         |

|   |      | 3.4.1  | Tracking devices inter-dependencies            |

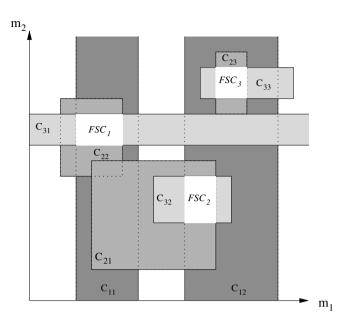

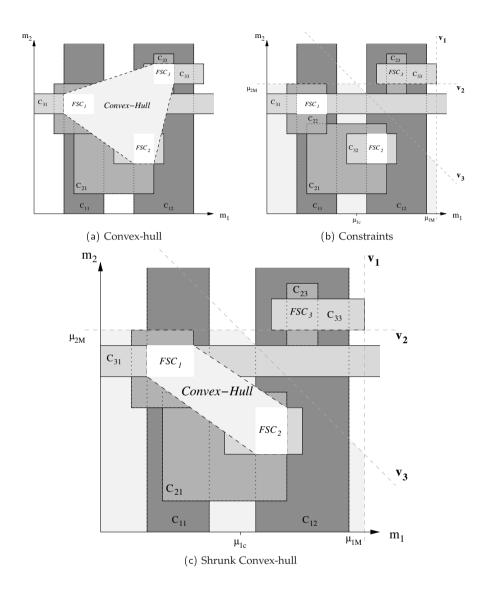

|   |      | 3.4.2  | Modeling Feasible Configurations               |

|   | 3.5  | The O  | ptimization Layer                              |

|   |      | 3.5.1  | Hierarchical distributed control 82            |

|   |      | 3.5.2  | A theoretical approach to the optimization     |

|   |      | 3.5.3  | An empirical approach to the optimization      |

|   | n    |        |                                                |

| 4 |      |        | onclusions and Developments 99                 |

|   | 4.1  |        | <sup>3</sup> 5                                 |

|   |      | 4.1.1  | Worst-case analysis                            |

|   |      | 4.1.2  | A safari on a real-world usage scenario        |

|   | 4.2  |        | usions                                         |

|   | 4.3  | Develo | opments                                        |

| Α | An   | [mplem | nentation Proposal 115                         |

|   | A.1  | -      | etical Concepts Implementation                 |

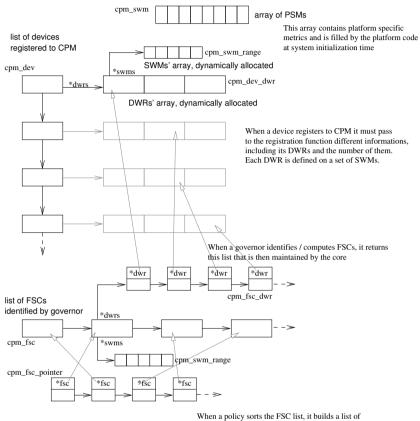

|   |      | A.1.1  | The System-Wide Metrics (SWMs)                 |

|   |      | A.1.2  | The Device Working Regions (DWRs)              |

|   |      | A.1.3  | The Feasible System-wide Configurations (FSCs) |

|   |      | A.1.4  | The objective function                         |

|   | A.2  |        | ramework Architecture                          |

|   | 11.2 |        | CPM Framework                                  |

|   |      | A.2.2  | Device drivers                                 |

|   |      | A.2.3  | Platform code                                  |

|   | A 2  | 9      | ramework Workflow                              |

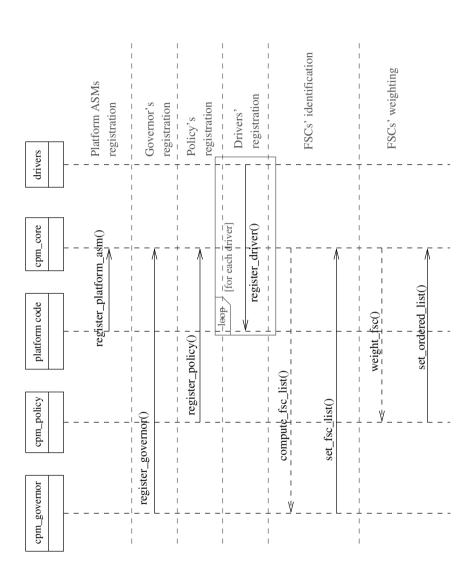

|   | A.3  | A.3.1  | The role of CPM at system initialization       |

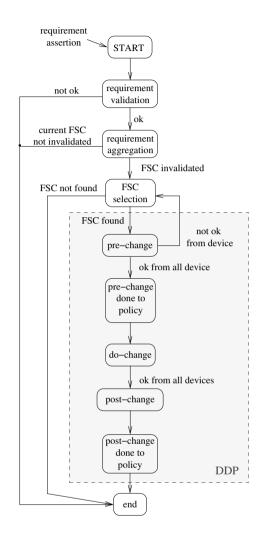

|   |      | 9      | The role of CPM at run-time                    |

|   | Λ.   | A.3.2  | ramework Interfaces                            |

|   | A.4  |        |                                                |

|   |      | A.4.1  | The basic data types                           |

|   |      | A.4.2  | The frameworks' core                           |

|   |      | A.4.3  | The user-space interface 133                   |

| A.5    | Gover            | nor and Policies Examples                 | 135 |  |  |  |  |

|--------|------------------|-------------------------------------------|-----|--|--|--|--|

|        | A.5.1            | The performance policy                    | 135 |  |  |  |  |

|        | A.5.2            | The exhaustive governor                   | 136 |  |  |  |  |

| B Ma   | in Linu          | x Frameworks for Power Management         | 139 |  |  |  |  |

| B.1    |                  | works Classification                      | 140 |  |  |  |  |

| B.2    | Pure-0           | OS Techniques                             | 141 |  |  |  |  |

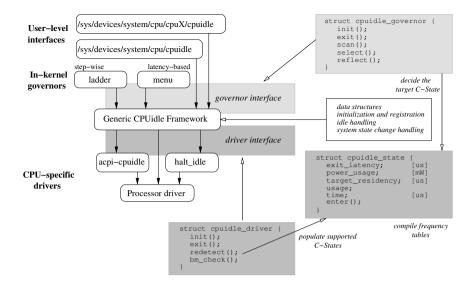

|        |                  | CPUidle: Do Noting Efficiently            |     |  |  |  |  |

|        |                  | CPUfreq: Use Just the Right Power         |     |  |  |  |  |

|        | B.2.3            | The Suspend/Resume Framework              |     |  |  |  |  |

|        | B.2.4            | The Clock Framework                       | 145 |  |  |  |  |

|        | B.2.5            | The Voltage and Current Control Framework |     |  |  |  |  |

| B.3    | Cross-           | Layer Techniques                          | 149 |  |  |  |  |

|        | B.3.1            | DPM: A centralized Approach to PM         |     |  |  |  |  |

|        | B.3.2            | QoSPM: A distributed Approach to PM       | 151 |  |  |  |  |

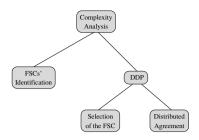

| C Co   | mputati          | onal Complexity Analysis                  | 153 |  |  |  |  |

|        |                  | y overview                                |     |  |  |  |  |

|        |                  | ique analysis                             |     |  |  |  |  |

|        |                  | FSC identification                        |     |  |  |  |  |

|        |                  | FSC selection                             |     |  |  |  |  |

|        |                  | Distributed agreement                     |     |  |  |  |  |

| Biblio | Bibliography 159 |                                           |     |  |  |  |  |

# Abstract

Resources management, and thus also energy saving, has become a high priority design goal for embedded multimedia mobile devices such as smartphones. Such devices are usually based on platforms using a System-on-Chip (SoC), which embeds a number of peripherals sharing some resources and competing on their usage. Each one of these many embedded devices are usually characterized by a set of working modes, each one corresponding to different profiles of power consumption and corresponding performances.

Modern consumer electronics products provide also multiple functionalities, ranging from classic phone calls to more complex use-cases which could involve network access and multimedia data processing such as audio-video decoding and playback. These multiple usage scenarios are usually characterized by a competition on the limited resources available and thus could also involve conflicting requirements on the underlying hardware. Therefore, a proper resources and power management of such new generation platforms has become a more and more complex added value.

The ultimate goal of such a management is the search of the optimal trade-off between power saving and performances perceived by the user. Thus, it is worth to treat it as an *optimization problem* and investigate on the definition of solutions that are easily portable among different products.

In the light of these considerations, to effectively support the optimization of a complex platform, it is necessary (i) to have an updated and system-wide view of the available resources, (ii) to collect and aggregate QoS requirements defined by the multiple running use-case scenarios and (iii) to exploit these information within a dynamic system-wide optimization policy.

This problem is not effectively solved by current approaches. A number of frameworks has been developed that focus on specific subsystems or even single devices. These approaches result in multiple optimization strategies being implemented within the same system, with the consequent risk of overlapping control actions and conflicting decisions. Thus, these specialized frameworks used alone cannot grant system-wide optimizations.

The user-space approaches that have been investigated solve this problem by means of a centralized resource and power manager which is implemented as a middleware between the applications and the operating system. Unfortunately, these approaches require to modify applications, which is not always possible. Moreover, being implemented outside the operating system they are to much abstract to efficiently exploit all the underlying hardware capabilities.

Finally, the cross-layer frameworks implemented in the past are too complex to be effectively used in production devices or too simple to produce interesting results.

In this work, I propose a novel methodology which is able to efficiently support both resources management and power optimizations without affecting userperceived performances. With the proposed approach, we avoid to design a centralized system-wide controller and to completely re-design it once the architecture or some of its hardware components changes. Instead, a single global optimization policy is designed to provide a coarse-grained tuning for already existing lowlevel and device-specific optimization policies. Indeed, this policy is designed to find a system-wide solution to the power consumption vs perceived performances problem. The solution is configured as a set of constraints that are notified to the multiple underlying device-specific and fine-tuning policies.

This methodology leverage a hierarchical design where specific domain experts could concentrate only on the definition of local optimization policies, targeting single subsystems or devices, by exploiting run-time information coming from the global policy. This global optimization policies take care also of collecting and aggregating resources requirements from applications, thus providing a complete and efficient in-kernel implementation of the cross-layer approach.

A framework implementing the proposed methodology has been developed and integrated within the mainline Linux kernel. Its design has been defined both to be efficient and to simplify the integration of both new and existing local control policies. The experimental results show that our implementation exhibits negligible run-time overheads while allowing to track correctly resources usage and identifying opportunities for power optimizations that do not impact on perceived performances.

# Estratto in lingua italiana

La gestione delle risorse, ed in particolare il risparmio energetico, sono fra gli aspetti critici nella progettazione di dispositivi embedded multimediali portatili come i telefoni cellulari di nuova generazione. Tali dispositivi sono di solito basati su piattaforme System-on-Chip (SoC), costituite da una serie di periferiche che condividono alcune risorse e competono per il loro utilizzo. Ciascuna di queste periferiche interne al SoC è generalmente caratterizzata da più modalità di lavoro, corrispondenti a diversi profili di consumo energetico e prestazioni.

Questi moderni dispositivi portatili supportano ormai un numero sempre maggiore di funzionalità, e non si limitano più alle classiche attività correlate alla gestione delle chiamate telefoniche. Scenari di utilizzo ben più complessi sono ormai all'ordine del giorno e possono coinvolgere l'accesso ad Internet e l'elaborazione di dati multimediali, come nel caso della riproduzione di contenuti audio e video. Questo tipo di applicazioni sono generalmente caratterizzate da una maggiore competizione per l'uso delle limitate risorse a disposizione, addirittura potrebbero anche implicare requisiti contrastanti sull'hardware sottostante. Pertanto, sebbene la gestione delle risorse e della potenza sia indubbiamente un valore aggiunto per i dispositivi mobili di nuova generazione, una sua corretta implementazione sta anche diventando sempre più complessa e richiede lo sviluppo di adeguate metodologie.

Alla luce di queste considerazioni, al fine di supportare efficacemente l'ottimizzazione di piattaforme complesse, è necessario (i) avere una visione complessiva ed aggiornata dello stato del sistema e delle risorse disponibili, (ii) raccogliere e aggregare opportunamente i requisiti di qualità di servizio definiti dai molteplici scenari d'uso in esecuzione, ed infine (iii) utilizzare queste informazioni all'interno di una opportuna politica di ottimizzazione globale del sistema. L'obiettivo finale del sistema di gestione sarà la ricerca del compromesso ottimale tra risparmio energetico e prestazioni percepite dall'utente. Si tratta quindi di un *problema di ottimizzazione* che richiede soluzioni che siano non solo efficaci ma anche facilmente adattabili a differenti ambiti applicativi e dispositivi.

Purtroppo, questo problema non è ancora stato risolto in modo soddisfacente.

Un certo numero di politiche di ottimizzazione sono già state sviluppate, principalmente concentrandosi su sottosistemi specifici o addirittura singole periferiche. Questi approcci hanno comportato l'impiego di strategie di ottimizzazione multiple all'interno di uno stesso sistema, con il conseguente rischio di sovrapposizione delle azioni di controllo o ancora peggio della possibilità di decisioni contrastanti e quindi potenziali instabilità del sistema. Altri approcci hanno cercato di affrontare il problema in spazio utente per lo più proponendo dei controllori centralizzati realizzati da uno strato software che si frappone fra le applicazioni ed il sistema operativo. Tali tecniche richiedono però generalmente un'opportuna modifica delle applicazioni, cosa non sempre possibile. Inoltre, essendo esterni al sistema operativo l'elevata astrazione rispetto alla piattaforma sottostante non consente di sfruttare appieno le capacità offerte dall'hardware. Infine, gli approcci così detti cross-layer implementati in passato sono troppo complessi per poter essere utilizzati proficuamente in dispositivi commerciali oppure troppo semplici per garantire risultati interessanti.

Questo lavoro propone una nuova metodologia in grado di supportare efficacemente il problema di ottimizzazione energetica e gestione delle risorse senza impattare negativamente sulle prestazioni percepite dall'utente. L'approccio proposto evita di dover progettare un nuovo sistema di controllo centralizzato ogni volta che si cambia piattaforma o anche un solo suo componente. Infatti, una singola politica di controllo centralizzata può essere progettata per interagire con pre-esistenti politiche di controllo locale di più basso livello fornendogli dei parametri di calibrazione. Infatti, tale politica centralizzata è definita per l'individuazione di una soluzione ottimale globale del problema di bilanciamento dei consumi energetici rispetto alle prestazioni percepite dall'utente. Tale soluzione si configura come un insieme di vincoli che possono essere notificati alle sottostanti politiche locali deputate invece al controllo fine dei singoli dispositivi.

La metodologia proposta si basa quindi su un approccio gerarchico al problema di controllo. In tal modo gli esperti di ciascun dispositivo possono concentrarsi sulla definizione delle relative politiche di ottimizzazione locale che possono però sfruttare durante la loro esecuzione le informazioni rese disponibili in modo trasparente dalla politica di ottimizzazione globale. La politica di ottimizzazione globale si occuperà inoltre di raccogliere ed aggregare opportunamente le richieste d'utilizzo delle risorse avanzate dalle applicazioni, realizzando quindi una completa ed efficiente implementazione in kernel-space degli approcci cross-layer.

Un framework che implementa la metodologia proposta è stato sviluppato ed integrato nell'ultima versione del kernel Linux. Tale implementazione è stata progettata in modo da essere efficiente e semplificare l'integrazione di politiche di controllo locali sia nuove che pre-esistenti. I risultati sperimentali mostrano che la nostra implementazione ha un trascurabile impatto sulle prestazioni del sistema in esecuzione, consente di tracciare correttamente l'utilizzo delle risorse ed anche di identificare correttamente le opportunità di ottimizzazione energetica che non impattano sulla prestazioni percepite dall'utente.

#### l Chapter

# Overview

" Engineering is the art of directing the great sources of power in nature for the use and convenience of man." Thomas Tredgold

This chapter provides an overview of this thesis, including its goal, its motivation, its fundamental approach and the benefits it offers. It first motivates why embedded systems' designers need a new generation of system-wide power and performances optimization techniques, on the basis of the current context. From this context I will derive the requirements that such techniques must meet. Finally, I will show how these requirements derive precise research choices, leading to a specific technique, which I will adopt.

# 1.1 Designing embedded systems is getting more and more difficult

In the last fifty years we have assisted to a sustained growth in the ability of silicon manufacturers to fit more and more transistors in the same area, and to raise the clock frequency of their devices. The processing power made available by microprocessors and programmable devices grew accordingly. Gordon E. Moore was the first, in 1965 to recognize [1] that the transistor density was growing exponentially over the years, and to capture this observation in his famous "law", originally formulated as: *«The complexity for minimum component costs has increased at a rate of*

#### roughly a factor of two per year»<sup>1</sup>.

When Moore's Law remained in lockstep with classical Dennard scaling [2], which predicts faster, lower-power transistors at each fabrication node, the architectural focus on big, fast processors made sense. However, Dennard scaling ceased to provide big gains in speed and big reductions in power dissipation starting at the 90nm node [3]. Since then, CMOS circuits continue to get smaller but they don't get faster or drop in power consumption nearly as fast as they did before IC lithographies hit 90nm. Consequently, power dissipation and energy consumption started to become unmanageable at this node [4]. The problem is getting worse with each new process node. Embedded systems' designers must now adopt design styles that reduce system clock rates if they are to meet power and energy consumption goals.

Since some year big semiconductor vendors already offer multicore, symmetric multiprocessing (SMP) processors [5]. Each SMP core can run multiple, concurrent applications' threads. Such multicore processors were found first in large servers and laptops to run applications based on the "SAMD" (single application, multiple data) model. Nowadays a lot of interest, excitement, and worries are stimulated by the application of those same SMP multicore architectures also to embedded designs [6], where at a first instance we could believe that only few applications are actually "embarrassingly parallel".

The current performance improvement trend uses parallelism to motivate the development of architectures that combine both fine grained and coarse grained parallelism in systems with tens or hundreds of processors. These systems can be considered "manycore" processor systems, with the goal of achieving higher parallel code performance [7]. Manycore processor systems have tremendous potential for high-performance computing and scientific applications. However, these architectures are going to be explored not only to be used as accelerators in the design of tera-flop or peta-flop computers, but also in the domain of mobile multimedia embedded system [8]. Indeed, the significant increase in parallelism within a processor can lead many benefits including higher power-efficiency and better memory latency tolerance.

<sup>&</sup>lt;sup>1</sup>To read reprints of Gordon Moore's 1965 and 1975 papers along with recent commentaries on Moore's Law, see the September 2006 issue of the *IEEE Solid-State Circuits Society Newsletter*.

**Asymmetric multicore architectures** Multi-core technology is presently massively used on embedded systems addressed to the multimedia mobile market such as that of 'nettops' and 'smartphones'. In the embedded system world, by expanding architectural thinking beyond SMP multicore architectures, it was even before possible to uncover at least two kinds of easily used concurrency that exploit heterogeneous rather than homogeneous architectures.

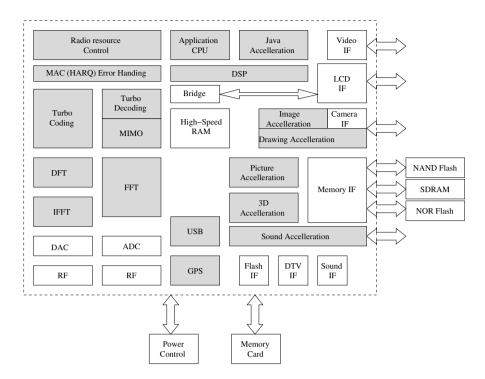

The first sort of parallelism is referred as "compositional concurrency" where various subsystems are woven together into a product. Each subsystem contains one or more processors optimized for a particular set of tasks. Communications within this architectural design style are structured so that subsystems interact only when needed. Figure 1.1 shows a block diagram of a Super 3G mobile phone that illustrates this idea. Compositional concurrent design offers many advantages:

- distributing computing tasks over several on-chip processors trades additional transistors in exchange for a lower clock rate to reduce overall power and energy consumption.

- dedicated subsystems can be powered down when not needed;

- application-specific instruction set processors (ASIPs) that are much more area and power efficient than general-purpose processors can be designed for each task processor;

- avoids the complex interactions and the synchronizations required between subsystems that are frequently associated with SMP hardware designs and multithreaded code;

The second form of convenient concurrency is referred as "pipelined dataflow", which is possible every time the computation can be divided into a pipeline built from individual task engines. Each pipelined task engine accepts, processes, and then emits data blocks. Once a processing task completes, the processed data block passes to the next engine in the chain. Such asymmetric multiprocessing algorithms appear in many signal and image processing applications<sup>2</sup>. Pipelining permits substantial concurrent processing and also allows even sharper application of ASIP principles because each processor in the pipeline can be highly tuned to just one part of the task.

These two types of convenient concurrency complemented each other. By combining the compositional subsystem style of design with pipelined, asymmetric multiprocessing (AMP) in each subsystem made it possible to built products in the consumer, portable, and media spaces with thousands of processors. Since many concurrent algorithms can be individually accelerated using compositionally concurrent design, and because many subsections of a single algorithm can be accelerated using pipelined design, the system problem becomes many pieces of code, all individually open to acceleration. The overall benefit of using multicore design has

<sup>&</sup>lt;sup>2</sup>e.g. from cell phone baseband processing to video and still image processing

Figure 1.1: The block diagram of a Super 3G mobile phone. There are 18 identified processing blocks (shown in gray) in the figure, each with a clearly defined task. It's easy to see how one might use as many as 18 processors (or more for sub-task processing) to divide and conquer this system design.

been therefore much greater than Amdahl's Law predicts, while the requirements for software development do not substantially change.

Of course there was a downside for these benefits. The cost for cleanly separating and accelerating multiple algorithms is an increase in the number of transistors per design, as realized through the use of multiple processors. That has always been a fundamental cost of the "divide-and-conquer" design approach. However, Moore's Law, which trumps Amdahl's Law in this situation, has ensured that the cost of more transistors is very low – and likely advantageous – with respect to the much higher costs associated with high system energy consumption and development complexity arising from multithreaded software.

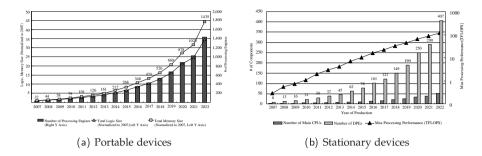

Figure 1.2: ITRS 2007 SoC consumer portable and stationary design complexity trends. Trend for the number of processing elements (PE's) predicted over the next 15 years in consumer portable devices, and the number of Data Processing Engines (DPE's) in consumer stationary devices.

**Emerging symmetric architectures** Programming AMP applications is far easier than programming multithreaded SMP applications because there are far fewer inter-task dependencies to worry about. Experience shows that it is possible to cleanly write software in this manner because many optimization issues arising from the use of multithreaded applications running on a limited set of identical processors are simply avoided. Therefore, by exploiting the two forms of "convenient concurrency" previously described it is possible to substantially free software developers from the need to think in terms of parallel operations because the various concurrent tasks are not so closely linked.

Nevertheless, even if is has granted increased performances in this few past years, asymmetric parallelism seem to be no more sufficient to support the requirements for the more and more advanced applications of next generation devices. The International Technology Road-map for Semiconductors [4] has estimated, over the next 15 years, that the number of processing elements (PE's) will grow up to 1435 in consumer portable devices (Figure 1.2a), such as mobile phones with extensive media capabilities or digital cameras. According to the same report, the number of Data Processing Engines (DPE's) in consumer stationary devices, such as high end game playing machines, will grow up to 407 with one main CPU every 8 DPEs (Figure 1.2b).

To feature hundreds or even thousands of processing cores on a single-die manycore processor, the challenges of energy consumption and performance scalability must be addressed within a given die area budget. Current commercial designs focus on MIMD-style multicores built with rather complex cores. While such designs provide a degree of generality, they may not be the most efficient way to build processors for applications with inherently scalable parallelism. **Increased power consumption threats** One of the main threat to the feasibility of products exploiting the new technologies and applications presented above is the increased importance of their computational requirements, which immediately impacts on their energy consumption. Energy consumption has always been a parameter of extreme criticality in the design of all the embedded systems which depend on a limited source of energy.

First digital embedded system employed no or little software (written in assembly language), their consumed power depending on the different possible operating conditions was relatively negligible. Nowadays, the energy demands of an innovative application is increased a lot with respect of than it used to be years ago. Embedded system comprise large software components, written in high level languages, including a complete operating system with many different network stack and a middleware layer. The load imposed on the system by modern applications such as the decoding of natural or synthetic video sequences, is extremely dependent on the data, and largely variable over different conditions.

In the above scenario, the energy-efficiency of the software components is dramatically more important than in the past. The degree of energy optimization of the software running on a battery-powered embedded device can determine its commercial success, and in some cases indeed its feasibility. It is out of question that even a feature-rich portable product would be scarcely appealing to the customers, if its battery lifetime is short enough to makes it unusable.

Adequate SW support is required to properly exploit the complexity of new systems Nowadays one has to have really good eyesight to understand the trend analysis described so far. In the last couple of years the big "multicore" and MPSoC question has been - how we program these devices? What programming models, tools and methods will exist to let us cope with 1400 processors? Will only the un-embarrassingly parallel applications be able to take use of this SoC complexity? Or can we find ways to make use of all this concurrent processing resource?

Rather than worrying about how to program a device with so many cores using today's thinking, we must be propositional and ask the questions - what kinds of new applications might be enabled with this kind of computing resource? Are there computational models impossible to implement effectively today that this kind of resource might enable?

All these open questions require to deepen invest on software. Has it always happens, hardware support anticipate some possibilities and than software designers are required to improve the system's software counterpart. This time the challenge is particularly tricky because of the different requirement that I have highlighted in the previous section.

Upcoming architectures need specifically designed multi-threaded software to exploit all the potentialities of their hardware parallelism. Multi-threaded software in turn will generally increase the overall applications complexity and relaying on abstraction layers seem to be the straightway to keep that complexity under control. This two aspects: software parallelization and layered abstraction are two of the most hot topic on actual system's software research.

**Software engineers are not parallel thinkers** Some researchers have created entirely new software languages that implicitly incorporate parallel programming structures [9]. But in this case the industry has proved itself highly resistant to the adoption of new programming languages. It appears to be very hard to train software programmers to think in terms of parallel, threaded operations.

More appealing appears to be the approaches that investigate on the automatic transformation of single sequential applications into multi thread at run-time [10]. These solutions allow not only to fit well to the large base of legacy software, but can also better support different evolving platforms thanks to their on-line tuning.

The recourse to a virtual execution environment, running on a multi-core processor, which is able to run complex, high-level applications and to exploit as much as possible the underlying parallel hardware, is going to be investigated on some recent works [11] and appears to be a promising approach to effectively tackle the problem of software parallelization.

**Operating System should better support user-space** To the Operating System (OS) is reserved a special role in the new architectures. Since the early days, the OS has always been the fundamental piece of abstraction from hardware. Being in the midway between more and more complex user-space applications and the upcoming multi- and many-core underlaying hardware architectures it can play an interesting role on better supporting layered abstraction.

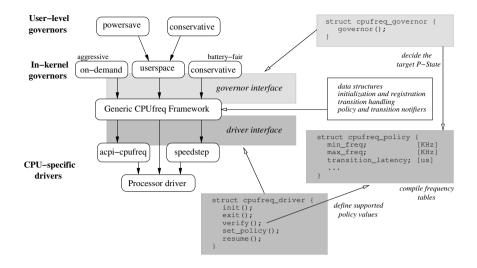

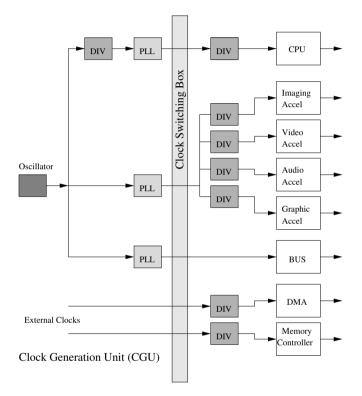

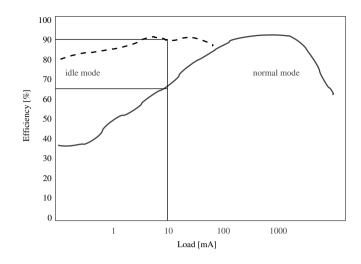

In the recent evolution of OS like Linux we noticed the introduction of quite advanced and sophisticated sub-system's specific controls based on local optimization policies. Tools such as CPUFreq [12], CPUIdle [13], the Clock framework [14] and the Voltage Control [15] frameworks are some of the most recent examples of fine detail but almost local controls available in recent kernels. These frameworks are able to enforce quite efficiently a precise control on specific platform subsystems such as CPUs or clock signals. Since the missing of a system-wide view of system resources and requirements, it could happens that these control take local decisions that produce side-effects on some other system components. Side-effects could compromise the quality of control either enforcing only sub-optimal configurations or, even worse, potentially introducing instability on the feed-back control loop.

The burden of bridging the gap, between the low level optimizations and the system complexity, and making possible system-wide optimizations, is entirely on the platform system developer's shoulders. In this regard, system-wide controls have been shown to produce the highest energy gains while hierarchical control systems are considered to be more safe and scalable.

### **1.2 Requirement for Power and Performances optimiza**tion techniques

In the previous section, I clarified and motivated the needs for this research starting from the market and technology's trends. This section is devoted to deriving the requirements starting from designers' needs.

Modern embedded system, especially those targeting multimedia mobile applications are base on more and more complex hardware platforms, providing many functionalities to support multiple and different usages of the same device. When designing and engineering these products, designers are required to provide support for system-wide optimizations that allow to get always good performances and energy consumptions trade-off considering all the competing running applications.

Supporting system-wide optimizations is crucial for many purposes, most notably: to allow multiple functionalities with different competing requirements to peacefully coexist on the same device, and to simplify the development of both applications and device drivers, by concentrating mainly on their functionalities. One of the crucial component interested on providing support for system-wide optimizations is for sure the Operating System (OS). This thesis deals with this very problem:

Define a possible system-wide power vs performances optimization strategy, to be implemented at Operating System level, that is sufficiently portable among different platforms without compromising too much its accuracy and efficiency, in all possible different device usage scenarios.

There are two reasons why I focus my attention to the Operating System level rather than trying to achieve the same optimizations at a different abstraction level: the first reason is that more abstract approaches usually have a lower efficiency and portability; the second reason is that for some specific subsystems the state of the art already provides support for effective local optimizations. I will motivate this claim in the following chapters.

As far as system-wide management is concerned, a platform-independent and general support is still missing and thus a new generation of high-level optimization tools is needed. Applications are becoming larger, more complex and dynamics, and then available optimization solutions are not keeping the pace. I will provide details for all of these claims in the next sections.

With respect to the problem of having a system-wide power vs performances optimization management, new designs need solutions which satisfy the following requirements:

- 1. system-wide;

- 2. fine detail;

- 3. dynamic;

- 4. scalable;

- 5. low-overhead;

The following paragraphs clarify what I mean by each of the above requirements. Chapter 2 will show that none of the current approaches satisfies all the above requirements at the same time. Throughout all this thesis, the choices I will make while designing my methodology will be guided and constrained by the above requirement.

**System-wide optimization:** modern embedded systems, especially those designed for multimedia mobile applications, are based on complex architectures, with many hardware subsystems, and they provide multiple functionalities competing for shared resources. Techniques that only locally optimize each subsystem can be of little practical effect. To get overall system benefits, instead a systemwide approach is required, providing a suitable level of abstraction that don't limits portability while still allowing to keep under control all the specific platforms available resources.

**Fine detail:** usually different platforms have different subsystems with different available resources and capabilities. Tools that don't fit well with the underlaying system cannot be able to properly exploits its behaviors. Thus a rougher platform detail is insufficient to achieve good control performances because of the risk to miss some optimization opportunities. Tools must be able to exploit detailed description of platform capabilities while still avoiding to become platform-specific.

**Dynamic:** multimedia mobile devices are becoming more and more dynamic in nature. Different functionalities are provided by the same device which change its role quite frequently depending on the user needs. Moreover we can notice also increasing variability in the behavior of algorithms; the behavior of multimedia encoders and decoders depend more and more on the contents of the streams they process, and applications from many other domains like wireless and gaming show the same trends. Accordingly a good optimization tool must be able to smoothly adapt to frequently changing working scenarios (use-cases) and must be able to keep the actual input data into account.

**Scalable:** the complexity of devices is increasing continuously, many-core architectures are on the horizon and thus in the future the number of either symmetric and asymmetric processing engine within a single die is set to increase. New generation tools must be designed to be scalable to provide control solutions that can be easily adapted to increasing complex systems without compromising performances.

**Low-overhead:** optimization techniques should be sufficiently lightweight on monitoring the system and enforcing control decisions on it. Tools that impact too much on system behaviors risk to introduce high latency between system state observation and control actions. This could invalidate optimization actions or even worse it could cost more than what it try to optimize. Low-overhead tools are required, even at the expense of inferior accuracy.

All of the above constraints must be met while keeping reasonable good performances for the control problem of trade-off power vs performances. Relative control accuracy is important especially when designers need to compare alternative solutions. Absolute accuracy is important especially when designers want to evaluate the performance of a control solution on different architectures.

Unfortunately, as the sections dedicated to the related work will show, none of the approaches currently available tackle appropriately all the above requirements at the same time. For example, drivers based approaches does not fulfill the dynamism and system-wide requirements. Current user-space approaches do not satisfy the detail requirement. An informal summary of the above considerations is given by the table below:

| Abstraction | System<br>wide | Fine detail | Dynamic | Scalable     | Low<br>overhead |

|-------------|----------------|-------------|---------|--------------|-----------------|

| drivers     | X              | 1           | X       | 1            | 1               |

| centralized | $\checkmark$   | 1           | ×       | ×            | $\checkmark$    |

| application | $\checkmark$   | ×           | 1       | $\checkmark$ | ×               |

Table 1.1: How existing techniques fit the requirements for a good power and performances optimization tool

All these reasons motivate the crucial need for system-wide, fine-detailed, fast, dynamic and accurate operating system support for power and performances trade-off optimizations.

This thesis is dedicated to the research of a system-wide power vs performance optimization control which fulfill the above requirements.

#### 1.3 Why we focus on Linux

The choice of an Operating System in which implement our proposal for a new system-wide optimization techniques is a crucial element for this work. I don't want just to provide yet-another-theoretical algorithm but instead I want to show how the proposed technique can be effectively implemented on a real system.

The technique I propose is largely independent from the Operating System which it is applied. Although I show an instance of this technique which is implemented as a Linux kernel framework, the technique does not rely on any specific feature which is provided by Linux only. Porting the same technique to another operating system, especially those written in C languages, in most cases is just a matter of few interface changes.

Nevertheless, the choice of the Linux kernel for the particular instance of the technique which I show in this thesis demands some justification. I choose Linux because it is OpenSource and because Linux, in all of its flavors, is one of the

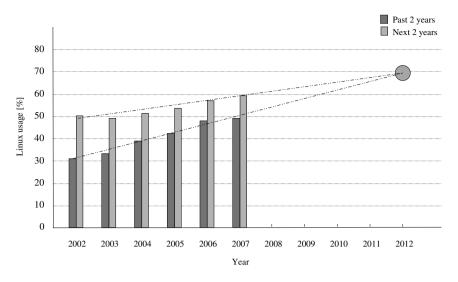

Figure 1.3: Actual and planned Linux use in the development of embedded systems may converge by 2012. Source: LinuxDevices.com.

leading operating systems in the embedded design community, and more and more embedded systems feature some Linux distributions.

Figure 1.3 present an interesting outcome from a study that covers the worldwide market for Linux employed in the development of embedded systems. This study has been conducted by the authoritative LinuxDevices.com website, dating back 2007 and compare the planned Linux use over the next two years, as well as actual use over the previous two. The study comments on the increasing use of Linux and forecast that this predominance is not to arrest soon, and motivate why:

«[...]in the early days, planned use far surpassed actual use. Today, as more and more project teams succeed in executing their Linux migration strategies, the Linux "uptake gap" has narrowed dramatically. Trend lines on the chart below suggest that by 2012, actual and planned Linux use will converge, at about 70 percent[...]

Interestingly, last year's survey data suggested that embedded Linux's uptake gap would close between 2009 and 2010 at closer to 60 percent. However, some 61 percent of this year's respondents plan to use Linux within two years, compared to 58 percent in the past two years – an increase that suggests Linux adoption may not level off as quickly as previously believed, and may achieve a greater overall market penetration than originally thought.»

The above figures and comments suggest that the diffusion of Linux kernel us-

age on embedded systems is still long, and that a system-wide power and performances optimization technique based on this Operating System, like the one proposed here, will be of great practical usefulness still for a long time to come.

#### 1.4 Many techniques are possible, just one is chosen

First, from now on I will generally use the term *framework* to denote an operating system's component that provide system-wide support for both power and performances optimizations. Carefully reducing overall system's power consumptions require a system-wide framework. Running concurrently resource-competing user-space programs while ensuring expected and perceived Quality-of-Services can take advantages from a system-wide framework support. All this thesis is about the definition of a system-wide framework, in this sense.

The goals for a system-wide power and performances control framework can be carried out in a variety of ways. The very purpose of such a framework is to "build a model" of the target system that can be used to identify the optimal system configuration according to run-time informations on resources availability and application's requirements. This is generally a complex process, which may involves also modeling how the underlying architecture works on different usage scenarios (use-cases).

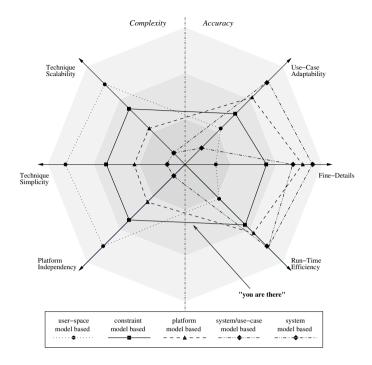

The properties of a model basically depends on the abstraction level we consider. More detailed models are more complex (therefore more difficult to build and to maintain, and slower to execute), but they may ensure better accuracy. All the possible modeling choices can be represented and compared in a complexity/accuracy space. Among these models, the ones which are non-Pareto-optimal do not deserve any further attention, because they are surpassed by some other model in both the objectives. The remaining ones generate a discrete (very large) set of models which I intuitively represent in Figure 1.4.

The Pareto-optimal solutions have been classified according to some evaluation indexes. I chose to focus on some index which are someway related to requirements identified in the previous section. The 'simplicity' index is an evaluation of how simple it is to "use" the framework both from the user-space perspective and the platform integration. The 'control precision' is quite self-explaining, it measure how good is the framework on approximating the real optimization goal avoiding local sub-optimal ones. The 'run time efficiency' is directly related to the 'low overhead' requirement, a framework is as much run-time efficient as much it don't affect on system performances which is trying to optimize. The 'platform independence' and 'scalability' indexes describe how well the framework can easily adapt to different platforms with almost minor modifications required and how it can easily scale with increasing system complexity. Finally the 'simplicity' index is an abstract evaluation of the framework implementation complexity. This last index has been explicitly considered because it is undoubted that conceptual simpler framework

Figure 1.4: Even after discarding the non-Pareto-optimal ones, many techniques to develop a system-wide optimization framework are possible. They exhibit different trade-offs between simplicity and accuracy. In this thesis I choose one, which is particularly suitable for multimedia mobile embedded systems.

are more probable to be endorsed by community and thus have higher probabilities to be well accepted and integrated within existing systems, e.g. the Linux kernel.

In the Figure 1.4 are compared with regard to these indexes, the main Paretooptimal techniques which can be identified in bibliography. Techniques based on a 'system model' (dash-dotted curve with rhomboidal points) are those that grant an overall maximum accuracy. These techniques usually relay on an off-line built model that capture the system behaviors and that can be used at run-time as a black-box controller where application requirements are the inputs and the optimal system-wide configuration is the output. Accuracy can be further improved, as indicated by a better 'use-case adaptability' index, when using a variant of these techniques which is based on 'use-case model'. In this case a system model is built for each use-case and selected at run-time by the control policy according to the specific working context. The main downside of these techniques is the complexity: building a system-wide model usually require extensive simulations in order to collect enough profiling data for post-process with some mathematical or statistical tool. The validation of a model also require an extensive work. Moreover, the models obtained are typically highly platform dependent and substantially unmodifiable without redo all the simulations. The end complexity is so high that usually these techniques are hardly adopted for multimedia mobile devices and are instead used on mission-critical embedded systems with longer life-time.

A significant complexity mitigation without compromising too much accuracy can be obtained using techniques based on a 'platform model' (dashed curve with triangular points). These techniques in the past have been effectively developed also for multimedia mobile devices, although they have not had a big spread. In this case the model is build as part of the platform-code and thus, being a software defined model, it can be modified and adapted to different platforms more easily. The main limitation is still the complexity because building the model require a detailed knowledge of all hardware subsystems.

The simpler techniques are those based on a 'user-space model' (dotted curve with round points). In this case the control policy is usually highly abstract from the underlying hardware and thus they require to trade accuracy for a reduced complexity. These techniques are easily portable among different platforms, usually even operating system independent and running as simple user-space applications. On the other hand, unfortunately these techniques usually show a too small accuracy to effectively support the aggressive optimization required by modern multimedia mobile devices.

A quite good trade-off between complexity and accuracy can be obtained using techniques based on a 'constraint model' (continuous curve with squared points), usually based on a distributed control policy that allows to reduce the complexity. Indeed, utilizing the principle of "divide and conquer", the complexity could be distributed on multiple modules such that each single one turns to be more simpler to define. This approach imply a modular design which improve scalability and portability too. The accuracy of that models with respect to the system-model based ones is reduced but still acceptable for multimedia mobile devices. This is mainly due thanks to the relatively high fine-details level that are still possible to reach with such kind of solutions.

The space and time allowed by a doctoral thesis permits the complete analysis of just one of these many techniques. I choose to focus my attention on the "constraint model" approach. This choice has to main motivation: the lakes of an established and well defined framework of this type for the mobile multimedia embedded devices application context, and secondly because it show the most promising application possibilities in this specific application fields. In instance, the fundamental approach presented here can be extended and refined to support some levels of HW accelerations. Anyway these possibilities are just going to be investigated deeply and I will not support these claim in this documents, as it would require too much time and space.

### 1.5 The fundamental approach of this thesis

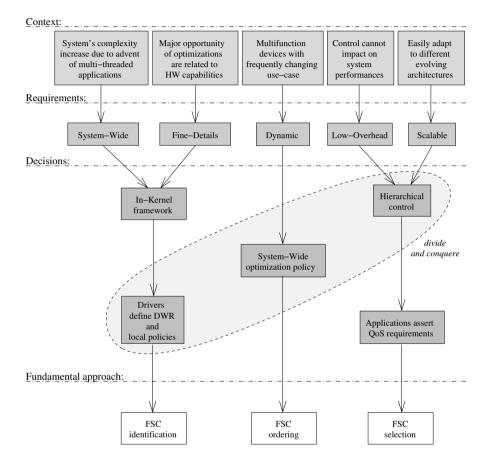

In this section I provide a quick overview of my approach. I summarize its fundamental steps and motivate their choice in terms of the requirements expressed in Sec. 1.2 on page 12. The same reasoning is also summarized in Fig. 1.5.

The 'system-wide' and 'fine detail' requirements motivate the decision to have an in-kernel framework. A framework at this level, which sit in between userspace applications and the bare hardware, can easily exploit the overall view on the system state while still not loosing too much details of the actual platform. Moreover kernel space already offers a set of highly efficient and optimized support functionalities that can be used for the implementation of a sufficiently lightweight optimization framework.

The low level details about the specific platform resources and capabilities are provided by both platform code and drivers, which are directly accessible by an in-kernel framework. The platform code, i.e. the architecture specific code that a kernel like Linux require to implement in order to have a very basic level of abstraction from the underlying hardware, can define a set of platform-specific metrics (PSM). These metrics represent platform configuration parameters to tune system behaviors and that are usually directly controlled by some drivers. Drivers in our view play a central role because they provide both some data to the optimization framework, where are used to reconstruct the specific system-wide view on capabilities and resources, and also implement highly efficient local optimization policies, which allow to have a fine control on the specific hardware.

The in-kernel framework is the perfect point to make a "divide and conquer" operation. Although it is not generally true that the coordination of local optimization policies leads to the same performances of a single centralized optimization control, this assumption leads to negligible worse while to the contrary show interesting benefits for overhead reduction and scalability of the solution. This motivate the decision to opt for a hierarchical control architecture, which has two kinds of control policies at different abstraction levels. Each driver implement its own low-level control policy, which is 'fine detailed' and 'low overhead'. A more abstract control policy is implemented by the in-kernel framework, which in turn is 'system-wide' and grants the 'scalable' requirement.

The framework's system-wide optimization policy satisfy the 'dynamic' requirement. This policy allows to implement a coarse-grained control that identify the high-level system-wide optimization strategy; which in instance could be either a performance boost or power reduction or even a mix between these two goals. Policies that are local to each driver provide fine tuning, within some operating mode enforced by the global policy, with very low run-time overhead and exploiting the 'fine details' knowledge about the controlled hardware. Moreover, the systemwide policy allows to dynamically adapt to changing working conditions by simply changing accordingly this policy. Different optimization goals can thus be enabled at tun-time.

Figure 1.5: How the fundamental approach of this thesis derives from the designers' requirements which, in turn, derive from the current context in the embedded design scenario.

From all these considerations and consequently decisions I have derived the fundamental approach of the technique developed in this thesis. This fundamental approach: accept inputs, yield outputs, and is composed as I describe below.

The technique shall get as inputs:

- a platform description, in terms of platform-specific system-wide metrics

- the driver capabilities, which define how each device mode maps on systemwide metrics

- an optimization policy, which can be changed at run-time and define the optimization goal

- QoS run-time requirements, either from user-space applications or platform subsystem, which define some constraint for the optimization problem

It shall yield as output an estimation of the optimal Feasible System-wide Configuration (FSC), taking into considerations resources availability and applications requirements.

It shall be composed of three fundamental phases:

- FSC identification

- FSC ordering

- FSC selection

More detailed explanations of the above steps follow.

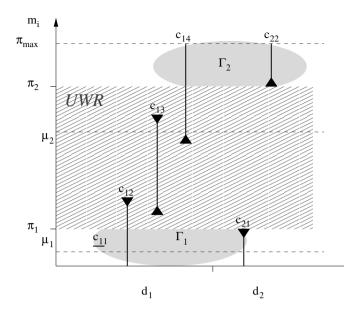

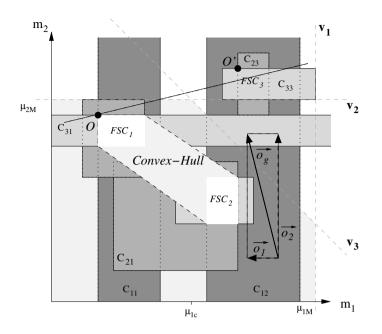

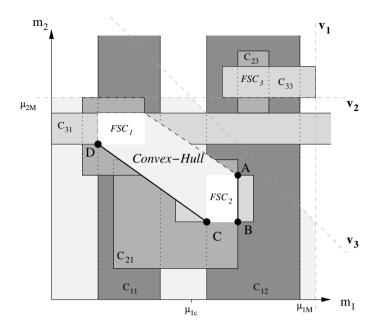

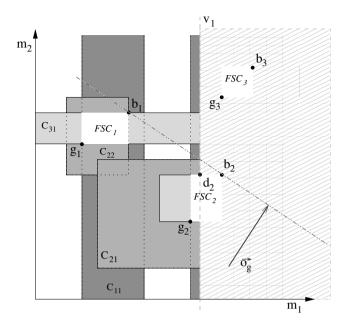

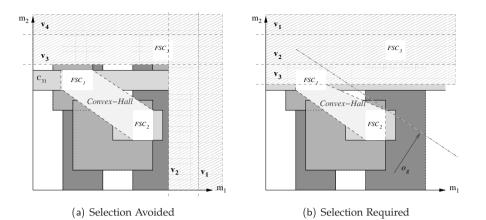

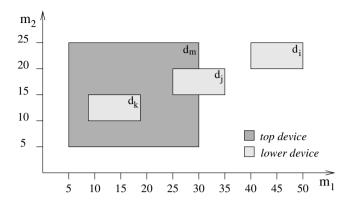

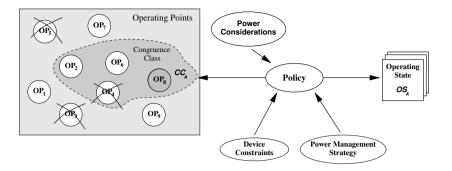

In the 'FSC identification' phase, the platform specific information collected both from platform-code and drivers are processed in order to automatically identify all the possible system-wide configurations which are feasible (FSC) for the specific platform. A FSC is defined by constraining a set of system-wide metrics while granting that all devices have an operating mode compatible with those constraints. This step is, in fact, one of the more complex topics of this work. I will show how this problem could be tackled and solved with different levels of efficiency.

In the 'FSC ordering' phase, a weight is associated to each identified FSC according to the running coarse-grained optimization policy. This weight is a measure of the optimality of an FSC with respect to that policy. Since policies can be changed dynamically to better adapt to different working conditions, in turn the weights also can change at run-time with respect to the new optimization goal.

In the 'FSC selection' phase, among all valid FSC just one is chosen, according to actual resource availability and optimization goal, and then enforced as the optimal system-wide configuration. At run-time, not all FSC identified during the first steps could be valid at any specific time. Applications or subsystem requirements could invalidate some of them. During this step the framework should be able to efficiently identify still valid FSC and select the optimal one.

### **1.6** The final objective of this thesis

In the light of all the above considerations,

this thesis researches a system-wide, fine-detailed, dynamic usecase adaptive, scalable and low-overhead framework to support the identification of an optimal trade-off between expected performances and reduce power consumptions on mobile multimedia embedded systems running a general purpose operating system.

The framework must be implemented on updated Linux kernel, exploiting already existing common facilities, and provide a simple interface that facilitate integration within existing device drivers. The define user-space interface should be platform-independent in order to support portability and minimize needs for modifications by developers. The framework should be able to suggest which are the optimal system-wide configurations according to actual available resources and competing use-space requirements. Moreover, as a further extension, the core framework should support design and configuration exploration which allow the inspection of eventually sub-optimal working modes and drive either software or platform redesign choices.

#### 1.7 A bird-eye-view on the proposed technique

In this section I provide an high-level view of the proposed approach.

The distributed control approach allow assumptions which facilitate modeling, more precisely: local policies are able to identify optimal device configurations give a set of constraints which usually change only at use-case changes. These assumptions are quite reasonable, especially when we look at multimedia mobile applications. In this specific case it's common to have highly specialized device drivers running fine tuning optimization policies and the typical usage of the device change during time but with a slower dynamics when compared to that of each single device.

These assumptions justify the recourse to a distributed control model, which is based on different levels of abstraction. Moreover, a distributed approach allows very good run-time accuracy, both in term of precision and overhead, while still not increasing to much the framework complexity, and thus avoiding to reduce scalability or portability.

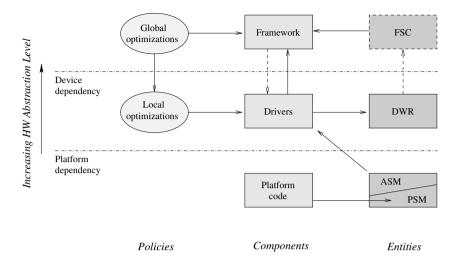

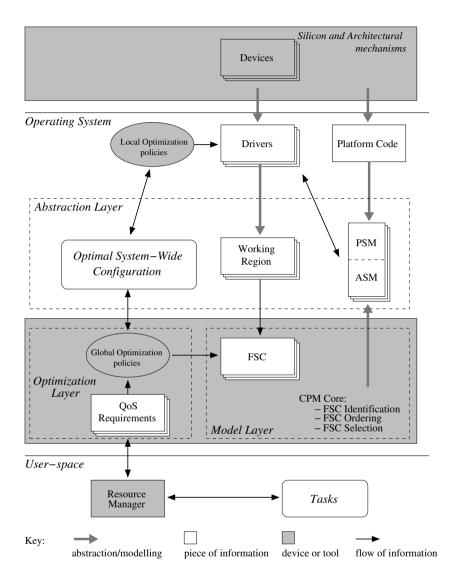

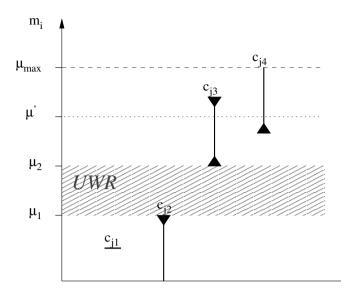

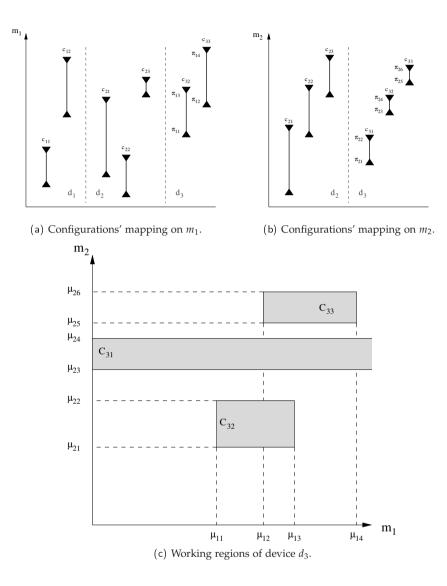

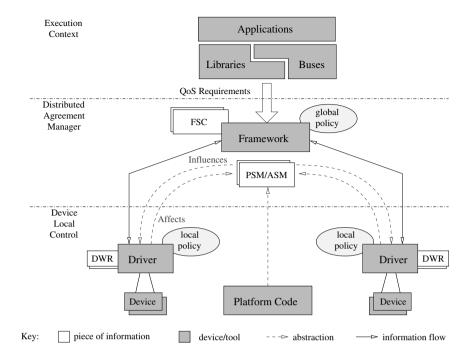

In Figure 1.6 is showed how different elements of the technique I propose correspond to different abstraction levels. The main elements are: *control policies*, operating system's *elements* and the *entities* introduced by the proposed framework. The lower level component is represented by the platform code, which could define some platform specific control parameter (i.e. Platform System-wide Metric, PSM) in addition to platform independent ones (i.e. Abstract System-wide Metric, ASM)

Figure 1.6: The proposed technique is developed at different abstraction levels. Lower levels exploit HW details to allow fine tuning while higher levels ensure system-wide optimization by exploiting run-time informations to derive coarse grained requirements for the lover levels. The different abstraction levels can be identified both on policies, operating system's components and framework defined entities.

defined by the proposed framework. At an higher level of abstraction we find local optimization policies, which are strictly related to device drivers. Each device driver could have its own fine tuning optimization policy and refer to System-wide Metrics (ASMs and PSMs) to define its operating modes (i.e. Device Working Regions, DWR). The maximum abstraction level is completely platform and devices independent and define global optimization policies. These policies, whit respect of local ones, are system-wide and thus will allow to exploit a complete system state view in order to identify the better trade-off between power consumptions and system performances. The framework code is in charge to run global optimization policies and enforce decisions to underlying drivers which could use them as some coarse grained optimization requirements. To properly run global policies the framework exploit the knowledge of all of the system feasible configurations (i.e. Feasible System-wide Configuration, FSC), which can be automatically identified starting from some informations about drivers and theirs working modes.

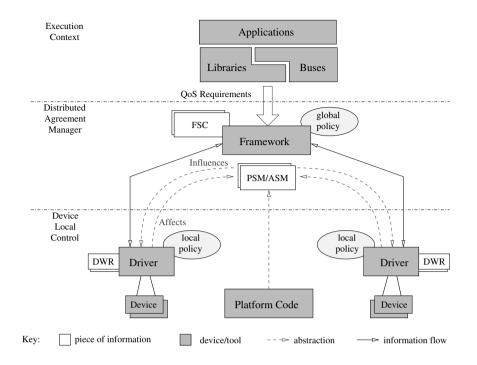

An overall view of the architecture for the proposed approach is showed in Figure 1.7, where: policies, operating system's components and entities are localized within the different software abstraction levels of a generic operating system. The framework along with the platform code define the set of available system-wide metrics (ASM/PSM), which in turn drivers refer to define theirs operating modes

Figure 1.7: A bird-eye-view of the proposed system-wide control architecture. The main system components are represented by platform code, drivers and the optimization framework code itself. These components either define or use some entities: system-wide metrics (ASM/PSM), device operating modes (DWR) and feasible system configurations (FSC). Policies are both locally and globally defined and are implemented as modular components so that can be changed at runtime.

(DWRs). Local policies can be associated directly to each driver while a global optimization policy is provided by the framework itself. Such an architecture provide a single and well defined interface to the userspace that can be used to collect Qualityof-Services (QoS) requests directly from a generic "execution context". The execution context is represented by applications, usually defining different use-cases, or better it can be represented by software libraries and buses. The eventually instrumentation of these last software components is particularly interesting because it allows to extend transparently the benefits of using such an optimization framework to all application using them.

### **1.8** Advantages of this approach

The approach proposed here offers a number of advantages with respect to its competitors:

• distributed control:

the framework I propose support a system-wide optimization based on a distributed control model. This approach allows to split frequently device specific fine tuning controls from less frequent coarse grained controls related to use-case changes. Single devices' fine tuning is demanded to drivers local policies which can exploit fine details knowledge about the underlying hardware. These local policies are constrained by system-wide requirements identified by a global optimization policy running at an higher abstraction level. The global optimization policy provide a coarse grained but systemwide control which ensure to identify global optimum configuration while still not impacting to much on overall system performances.

Moreover, distributed control allows also to allot control complexity on different components, basically on each device drivers, and support their local policies with just some constraints coming from a system state overall view. The distribution of the complexity also allows you to implement solutions that are modular and support composition and reuse of code. This at the end improve the simplicity and the portability of the final solution.

• improved portability:

the modular implementation of a distributed control model improve the portability to different platforms and systems, of an existing solution adopting the framework I propose. Indeed this requires to change only low-level components, usually drivers and their policies, to match the target system, while its possible to reuse the code for common components. Since the control model don't use a predefined system-wide model, but instead is able to automatically build such a model at run-time, the modeling effort is also reduced and substantially limited to drivers' local policies. This effort is worth done because at this level of abstraction not only it is possible to exploit fine-details, producing highly device-specific and optimized policies, but also the produced code will be reusable on all platforms using the same device. This is possible thanks to a properly defined interface between the proposed framework and drivers.

A domain expert could claim that in practice it is very difficult to extract the FSCs for all the components and the inter-dependencies between them, also considering that they all come from different vendors. Regarding this point it is worth to notice that, one of the main advantages of the proposed framework compared to others is rights its ability to compute automatically all these information. Moreover, this is done starting from much more simpler information which require only a restricted knowledge on single subsystems or device drivers.

• simple integration:

while the drivers' interface support code reuse on different platforms, a properly defined interface that the framework I propose expose to the user-space allows to increase even more platform independence for this side. The use of well defined interfaces to decouple software components simplify the integration of both drivers and user-space with the framework. Each software component will be required to implement only few and specific extensions in order to correctly take part to the optimization control.

• different level of abstraction:

the technique proposed exploits different levels of abstraction in order to implement a "divide and conquer" approach. The low levels of abstraction refer to specific components and can utilize their knowledge in order to finely adjust devices' operating modes. The more abstract components can instead use a comprehensive system view to ensure the achievement of a global optimization. The "different levels of abstraction" approach has been extensively adopted in the proposed techniques for the definitions of all its elements. Policies have been spitted in locals and global. Operating system's components range from low level platform code trough drivers up to the framework code and user-space applications. And finally, entities defined by the proposed techniques corresponds to different levels of abstractions with platform specific metrics (PSM) defined by the platform code, abstract metrics (ASM) and devices operating modes (DWR) defined by the drivers and finally the feasible system configurations (FSC) which are automatically identified by the framework.

The layered design of the proposed approach allows also to improve its runtime efficiency. Indeed, the framework require to run algorithms of different complexity ad different timeframes. The more complex operation is FSC identifications, but it is run just on time after system boot. An average complexity function is the FSC ordering, but it happens only when the optimization policy changes and this is a quite infrequent event. Moreover, this operation allows to speedup the most critical operation: the FSC selection. This is also the most efficient algorithm, with a very limited run-time overhead. Experimental results show that we could aim to handle a real system with a million of FSC with a negligible impact on performances.

• maintainability:

all the previous points contribute to simplify the maintainability of an implementation. Either changing/upgrading a single system component or considering a new use-case does not require extensive software modifications but only adjustments limited to the specific driver or corresponding software component. The framework then provides all the mechanisms to correctly reconstruct an updated system-wide state view and thus ensure the global optimization policy to run correctly.

• different working mode:

the proposed technique support different working modes to better fit target platform capabilities and progressive integration. A *best-effort mode* allows rapid prototyping when porting the framework on a platform with not all drivers integrated. In this mode the framework is still able to feed requirements to already integrated drivers supporting their local policy but not granting global optimization. A *distributed-agreement mode* instead can be enabled when all interested drivers are integrated with the framework and is able to identify global optimum and force drivers to always agree on a new feasible configuration once the use-case or system requirements changes.

integration with operating system: an implementation of the proposed framework has been developed and completely integrated within the Linux kernel. This will ensure a maintained code-base implementing the main mass of the whole framework, constantly revised and improved by the community. Moreover, new drivers policies, once developed end integrated are always available and ready-to-use for new platform's development thanks to the modular approach provided by the framework design.

### 1.9 Frequently raised objections

When working in a research area which is populated and commonly approached with a quite different mentality with respect to the relatively new approach you are advancing, it is often difficult to convince one's own audience about the novelty of his approach and its soundness. Power and performances trade-off for embedded system is for sure such a field. Additionally, in the specific topic covered by this thesis, research papers are relatively few and often "overclaim" their accomplishments in their titles, with respect to the actual contribution described in their texts. This practice pollutes the research concept space, inducing the idea that a problem was effectively solved when it was in fact just described, or tackled incompletely. Most of the time the complex problems we are facing is dissected and the research focus is only on specific subsystem, without considering the overall effects, or even worst basing the solution on a set of hypothesis which ten turns to be too much constraining to have a realistic and usable solution.

This section is designed to help reviewers not being mislead by these practices, and to anticipate criticism. It is therefore structured as a "Frequently Asked Questions" section of a manual. It is written in an informal, straight-to-the-point style. The reader will indulge me, as long as my claims are correct and motivated.

#### **1.9.1** «Your novel contribution is not quite clear»

This work has novelty in its objective, in its method and in its results. The scientific merit is obviously in the method. This technique is the first work which attempts the definition of a system-wide framework, for distributed control of the trade-off between power consumption and performances, actually implemented and verified, which accomplish that objective. The framework comprehensively considers all system's elements, at any abstraction level, without compromising neither performances nor precision thanks to a proper modular design.

#### 1.9.2 «CPM has already been implemented!»

Yes and no. The matter is ambiguous. It all depends on how you define "constrained power management". Since this ambiguity is a potential danger to understanding the contribution of this thesis, then I prefer to disambiguate the term.

I motivated above why new platform design need a technique to support the optimization of power consumption vs performances trade-off, and such technique must relay on a system-wide approach (i.e. it must identify global optimum). Because of this need, I define "constrained power management" the ability to identify system-wide optimal configurations, considering both different low-level capabilities and changing high-level resource requirements at the same time.

According with this definition, this thesis present **the first** constrained power management technique. No other techniques before have provided fine-grained control without resorting to lower level platform models (typically built by off-line profiling and usually considering only a limited number of sub-systems). On the other hand, all the techniques which addressed system-wide optimizations, were unable to consider neither fine-details for the configuration of devices or dynamic use-cases.

The terminology is debatable, you may apply broader definitions of the "constrained power management" term. In this case, a number of works in literature may be considered to have already applied this technique. Nevertheless, the above considerations must be kept clearly in mind, otherwise the novel contribution of this work is neglected just for lack of precision in terminology.

#### **1.9.3** «Your approach is too limited»

This thesis presents a broad methodology which define many components and some platform specific extensions, but it details only the core framework, the global optimization strategy and the interface for the extension. This instance is incomplete to be effectively used on a real-system but it completely define the overall common components so that the definition of extensions is simple and precisely defined. I did that because I want to stick to a good principle: do one thing, do it well. I claim that a solid but narrow theoretical foundation which may be extended with some effort is more desirable than a set of broader but less solid foundations. It is clear that in the scope and duration of a single Ph.D. thesis it is impossible to achieve breadth and solidity at the same time. That is obviously the ideal goal, but not practically achievable. To some extent, generality can be traded with accuracy, and I have chosen to privilege accuracy.

#### **1.9.4** «Your approach is too difficult to actually use it»

I hardly tried to keep simple the proposed techniques, indeed the integration simplicity is reasonably considered a key factor for the success of any new proposal. Nevertheless too much simple solutions hardly can grant good performances especially regarding control accuracy. All that considered one of my design constraints has been to better support a "divide and conquer" approach in order to spread the complexity too.

The main complexity of the proposed approach has been located within the framework core, where the global optimization policies and proper interfaces toward both user-space and drivers are implemented. What still remains on the platform designer's shoulders is just the platform specific code and the low-level device drivers' policies. It is worth to notice that those components are completely independent each other thanks to the modular design of the proposed approach. This allows to assign specific extensions to different and well prepared subsystem experts: each one could share his better knowledge of a specific device working modes with others by simply providing a self-contained integration to the frame-work. The framework itself will then provide all the necessary support to collect all those fine-detailed informations and exploit them the better is possible, compatibly to run-time available resources and use-case requirements, to ensure system-wide optimization in an almost completely transparent way.

# **1.10** The organization of this thesis